目录

5 Thread-Level Parallelism

5.1 Introduction

5.5 Synchronization: The Basics

5.6 Models of Memory Consistency: An Introduction

5.7 Cross-Cutting Issues

5.8 Putting It All Together: Multicore Processors and Their Performance

5.9 Fallacies and Pitfalls

5.10 The Future of Multicore Scaling

5.11 Concluding Remarks

6 Warehouse-Scale Computers to Exploit Request-Level and Data-Level Parallelism

6.1 Introduction

6.2 Programming Models and Workloads for Warehouse-Scale Computers

6.3 Computer Architecture of Warehouse-Scale Computers

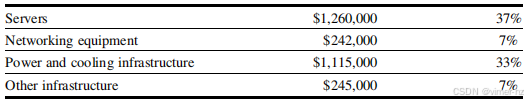

6.4 The Efficiency and Cost of Warehouse-Scale Computers

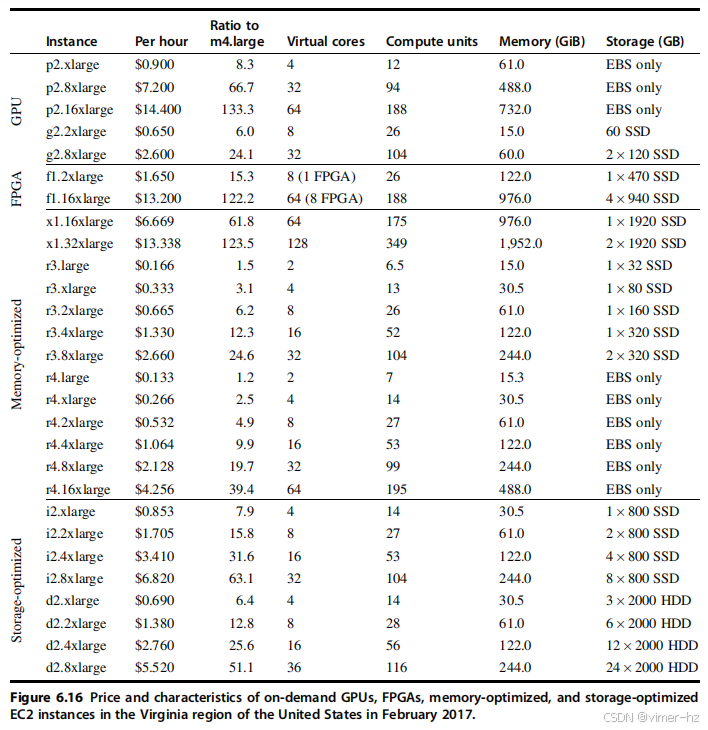

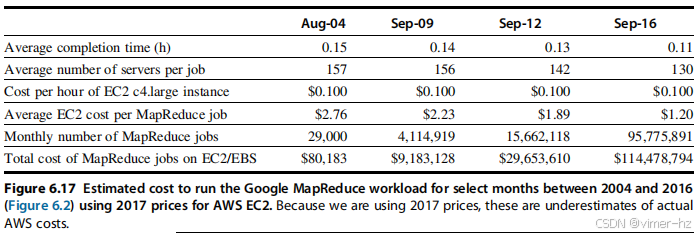

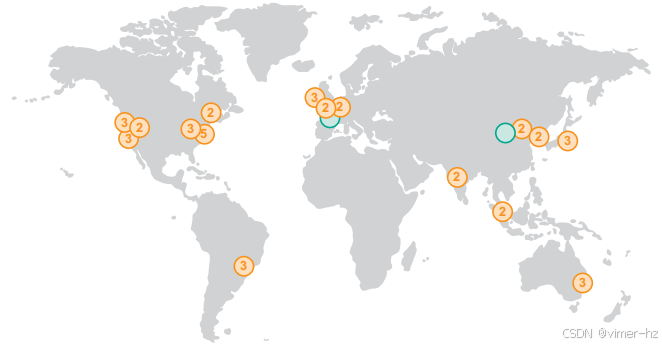

6.5 Cloud Computing: The Return of Utility Computing

6.6 Cross-Cutting Issues

6.7 Putting It All Together: A Google Warehouse-Scale Computer

6.8 Fallacies and Pitfalls

6.9 Concluding Remarks

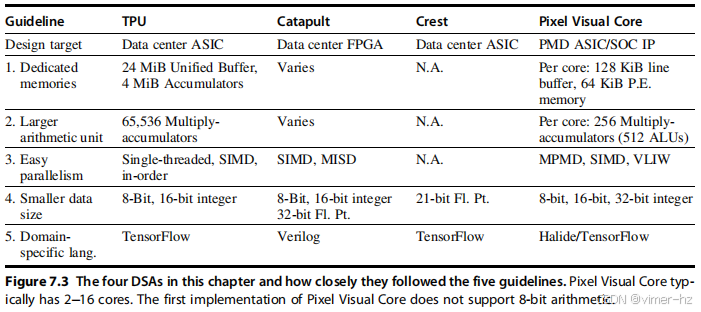

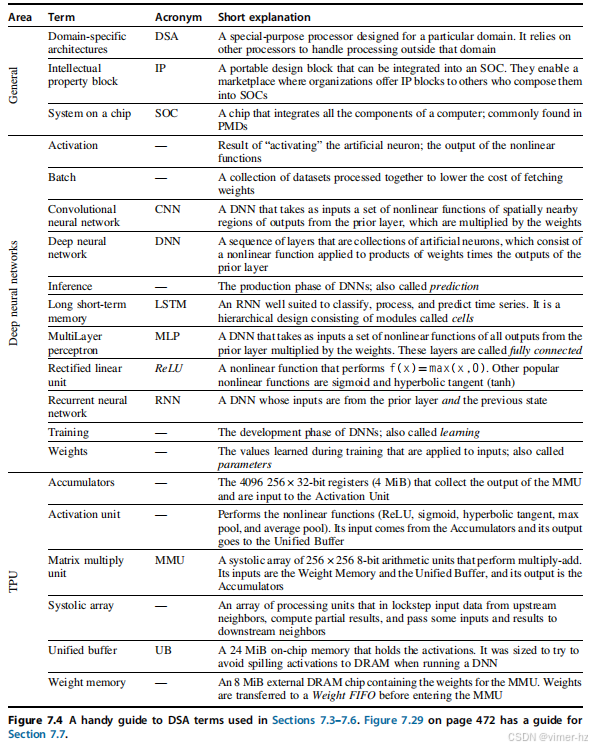

7 Domain-Specific Architectures

7.1 Introduction

7.2 Guidelines for DSAs

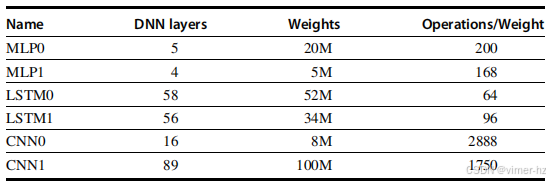

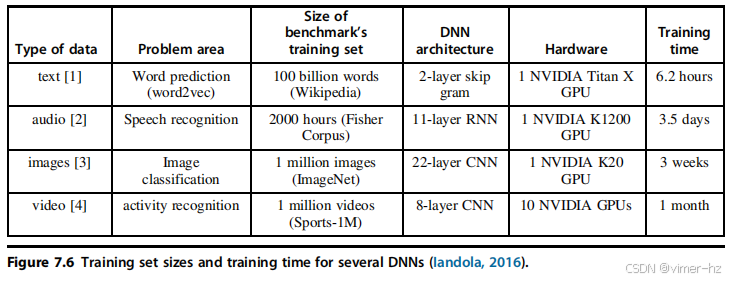

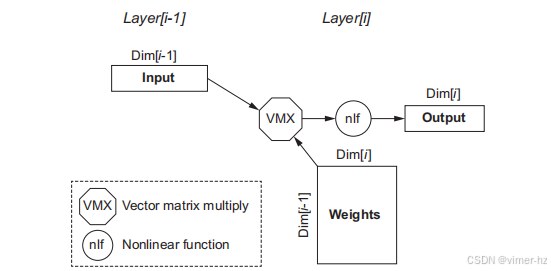

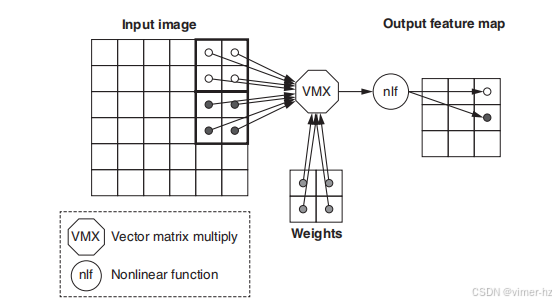

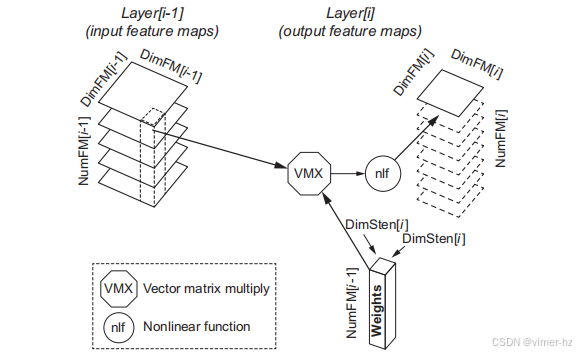

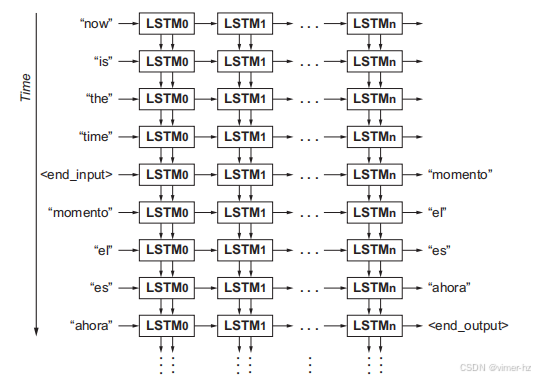

7.3 Example Domain: Deep Neural Networks

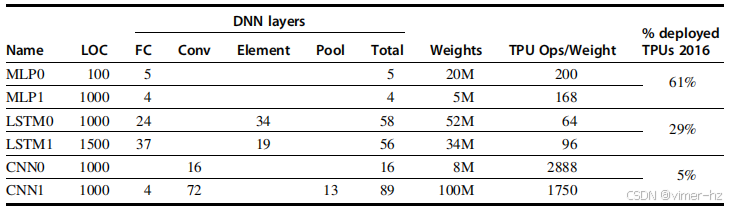

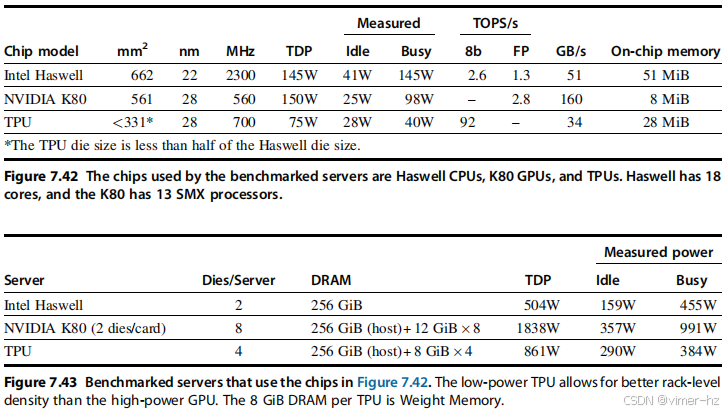

7.4 Google’s Tensor Processing Unit, an Inference Data Center Accelerator

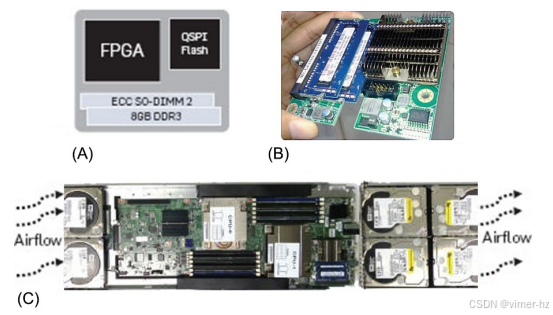

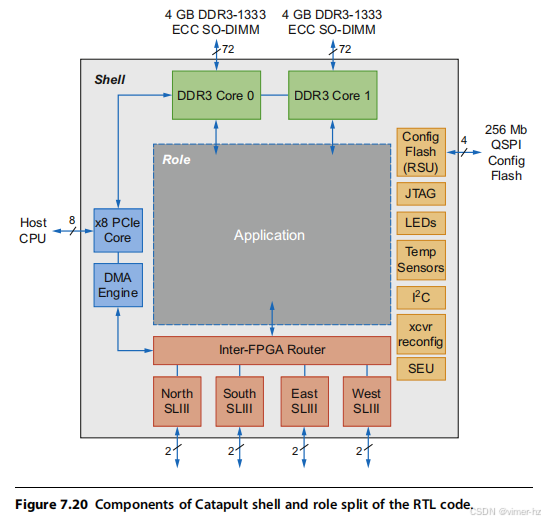

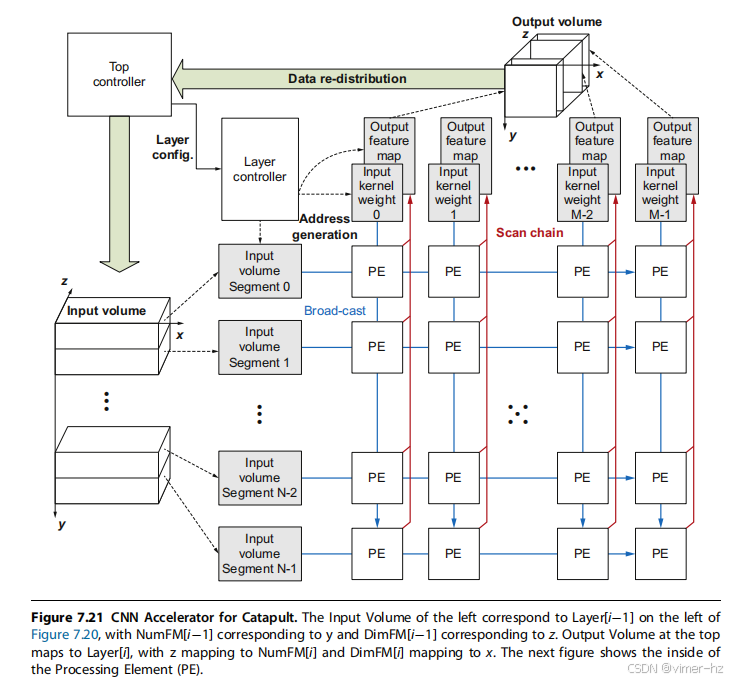

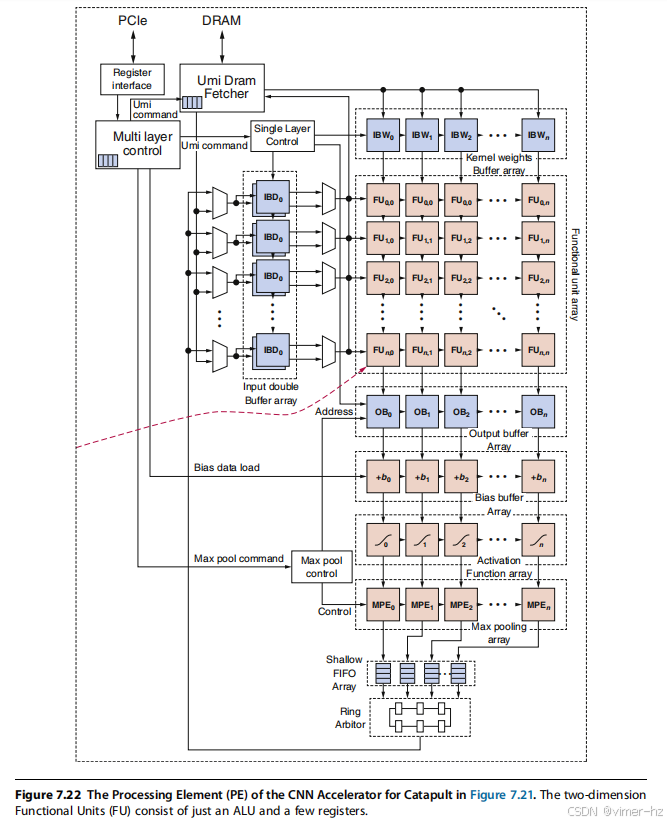

7.5 Microsoft Catapult, a Flexible Data Center Accelerator

7.6 Intel Crest, a Data Center Accelerator for Training

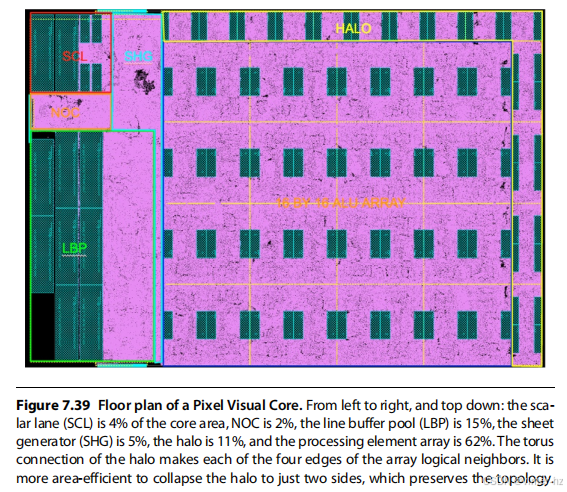

7.7 Pixel Visual Core, a Personal Mobile Device Image Processing Unit

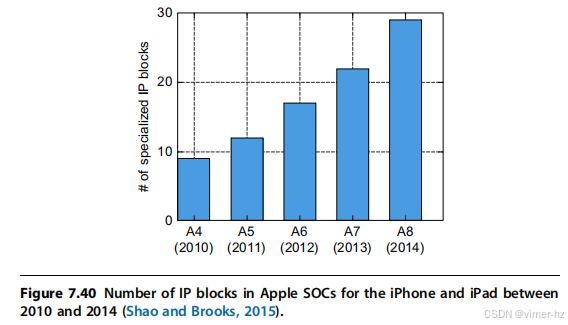

7.8 Cross-Cutting Issues Heterogeneity and System on a Chip (SOC)

7.9 Putting It All Together: CPUs Versus GPUs Versus DNN Accelerators

7.10 Fallacies and Pitfalls

7.11 Concluding Remarks

5 Thread-Level Parallelism

对传统组织结构的转变发生在20世纪60年代中期,当时在提高计算机操作速度的努力中,收益递减法则开始显现……电子电路的操作速度最终受到光速的限制……许多电路已经在纳秒范围内运行。

——W. Jack Bouknight 等,《Illiac IV 系统》(1972)

我们将所有未来的产品开发都专注于多核设计。我们相信这是行业的一个关键转折点。

——英特尔总裁保罗·奥特林尼,在2005年英特尔开发者论坛上描述英特尔的未来方向

自2004年以来,处理器设计师增加了核心数量,以利用摩尔定律的扩展,而不是专注于单核性能。丹纳德缩放失效,部分是对向多核部件转变的响应,可能很快会限制多核扩展,就像单核扩展已被遏制一样。

——Hadi Esmaeilzadeh 等,《功率限制与暗硅挑战多核的未来》(2012)

5.1 Introduction

正如本章开头的引用所示,一些研究人员已经认为单处理器架构的进展即将结束。这种看法显然是过早的;实际上,在1986年至2003年期间,由微处理器驱动的单处理器性能增长达到了自20世纪50年代末和60年代初第一台晶体管计算机以来的最高水平。尽管如此,随着设计师寻求一种方法来构建能够实现比单个微处理器更高性能的服务器和超级计算机,同时利用商品微处理器的成本效益优势,多处理器的重要性在90年代不断增长。正如我们在第1章和第3章中讨论的,由于在利用指令级并行性(ILP)方面收益递减的放缓,加上对功耗日益严重的担忧,导致了计算机架构进入了一个新时代——一个多处理器从低端到高端都扮演重要角色的时代。第二个引用准确捕捉了这一明显的转折点。

多处理器重要性增加反映了几个主要因素:

- 在2000年至2005年间,设计师试图发现和利用更多ILP时遇到的硅和能源使用效率显著降低,结果证明这种做法是低效的,因为电力和硅的成本增长速度快于性能。除了ILP,我们所知道的唯一可以快速提高性能的方法(从切换的角度来看)是通过多处理。

- 随着云计算和软件即服务变得越来越重要,对高端服务器的兴趣日益增长。

- 数据密集型应用的增长,受益于互联网上海量数据的可用性。

- 对桌面性能的提升关注减少(至少在图形之外),要么是因为当前性能可以接受,要么是因为高度计算和数据密集型的应用正在云端进行。

- 对如何有效使用多处理器有了更好的理解,尤其是在存在大量数据集(通常以数据并行性形式)、科学和工程代码中的“自然世界”并行性或大量独立请求之间的并行性(请求级并行性)等显著固有并行性的服务器环境中。

- 通过复制而不是独特设计来利用设计投资的优势;所有多处理器设计都提供这样的杠杆作用。

第三个引用提醒我们,多核可能仅提供有限的性能扩展可能性。阿姆达尔法则的影响与丹纳德缩放的结束意味着,多核的未来可能受到限制,至少在单个应用程序的性能扩展方面。我们将在本章后面再次讨论这个主题。

在本章中,我们重点关注利用线程级并行性(TLP)。TLP意味着存在多个程序计数器,因此主要通过多指令多数据流(MIMD)来利用。尽管MIMD已经存在了几十年,但线程级并行性在从嵌入式应用到高端服务器的各类计算中走到前沿是相对较新的现象。同样,广泛应用于各种通用应用程序的线程级并行性,相较于事务处理或科学应用,也较为新颖。

我们在本章的重点是多处理器,我们将其定义为由紧密耦合的处理器组成的计算机,这些处理器的协调和使用通常由单一操作系统控制,并通过共享地址空间共享内存。这种系统通过两种不同的软件模型利用线程级并行性。第一种是执行一组紧密耦合的线程协同完成单一任务,通常称为并行处理。第二种是执行多个相对独立的进程,这些进程可能源自一个或多个用户,这是一种请求级并行性,尽管其规模远小于我们在下一章探讨的内容。

请求级并行性可以通过在多个处理器上运行的单一应用程序来实现,例如数据库响应查询,或通过多个独立运行的应用程序来实现,通常称为多程序设计。

我们在本章考察的多处理器通常从双处理器到数十个甚至数百个处理器不等,通过共享内存进行通信和协调。虽然通过内存共享暗示了共享地址空间,但并不一定意味着只有一个物理内存。这类多处理器包括多个核心的单芯片系统,称为多核,以及由多个芯片组成的计算机,每个芯片通常也是多核的。许多公司制造这种多处理器,包括惠普、戴尔、思科、IBM、SGI、联想、甲骨文、富士通等。

除了真正的多处理器外,我们还将讨论多线程技术,该技术支持多个线程在单个多发射处理器上以交错方式执行。许多多核处理器也包含对多线程的支持。

在下一章中,我们将考虑由大量处理器构建的超大规模计算机,这些处理器通过网络技术连接(不一定是用于将计算机连接到互联网的相同网络技术),通常称为集群;这些大规模系统主要用于云计算,执行大量独立任务并行处理。最近,像搜索和某些机器学习算法等可以轻松并行化的计算密集型任务也利用了集群。当这些集群增长到数万台服务器及以上时,我们称之为仓库级计算机。亚马逊、谷歌、微软和Facebook都制造仓库级计算机。

除了我们在这里研究的多处理器和下一章的仓库级系统,还有一系列特殊的大规模多处理器系统,有时被称为多计算机。这些系统的耦合性通常低于本章讨论的多处理器,但通常高于下一章的仓库级系统。这类多计算机的主要用途是在高端科学计算中,尽管它们有时也用于商业应用,填补多处理器和仓库级计算机之间的空白。Cray X 系列和 IBM BlueGene 是这些多计算机的典型例子。

许多其他书籍,如 Culler 等(1999),详细介绍了这些系统。由于多处理领域的庞大和不断变化(刚提到的 Culler 等参考书超过 1000 页,仅讨论多处理!),我们选择将注意力集中在我们认为最重要和通用的计算空间部分。附录 I 讨论了在大型科学应用背景下构建此类计算机时出现的一些问题。

我们的重点将放在大约有 4 到 256 个处理器核心的多处理器上,这些处理器可能占用从 4 到 16 个独立芯片。这样的设计在单位数量和经济价值上都占据主导地位。在大规模多处理器中,互连网络是设计的关键部分;附录 F 专注于这一主题。

### 多处理器架构:问题与方法

为了利用具有 n 个处理器的 MIMD 多处理器,我们通常需要至少有 n 个线程或进程来执行;在大多数现代多核芯片中,利用多线程,这个数字通常会增加 2 到 4 倍。单个进程中的独立线程通常由程序员识别或由操作系统创建(来自多个独立请求)。在另一种极端情况下,一个线程可能由几十次循环迭代组成,这些迭代是由一个并行编译器生成的,利用了循环中的数据并行性。

尽管分配给线程的计算量(称为粒度)在考虑如何高效利用线程级并行性时非常重要,但与指令级并行性的一个重要定性区别在于,线程级并行性是在软件系统或程序员的高层次上识别的,且线程包含数百到数百万条可以并行执行的指令。

线程还可以用来利用数据级并行性,尽管其开销通常高于 SIMD 处理器或 GPU(见第 4 章)。这种开销意味着粒度必须足够大,以便有效地利用并行性。例如,尽管向量处理器或 GPU 能够有效地对短向量的操作进行并行化,但当并行性分布在多个线程之间时,结果的粒度可能会小到开销使得在 MIMD 中利用并行性变得过于昂贵。

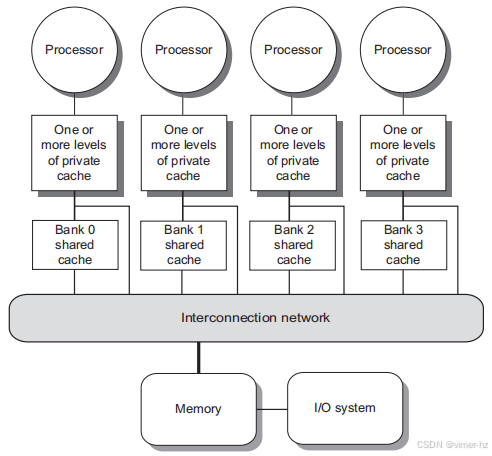

现有的共享内存多处理器可以分为两类,具体取决于涉及的处理器数量,这又决定了内存组织和互连策略。我们根据内存组织来称呼多处理器,因为什么构成小数量或大数量的处理器随着时间的推移而不断变化。

第一组我们称之为对称(共享内存)多处理器(SMPs),或集中式共享内存多处理器,通常具有小到中等数量的核心,通常不超过32个。对于处理器数量如此之少的多处理器,处理器可以共享一个所有处理器都能平等访问的单一集中式内存,因此称之为对称。在多核芯片中,内存通常在核心之间以集中方式共享;目前大多数现有的多核处理器都是SMP,但并非所有。(注意,有些文献错误地将SMP用作共享内存处理器的缩写,但这种用法是不正确的。)

一些多核处理器对最外层缓存的访问是非均匀的,这种结构称为非均匀缓存访问(NUCA),因此即使它们有单一主内存,也不能真正称为SMP。IBM Power8具有分布式L3缓存,对L3中不同地址的访问时间是非均匀的。

在由多个多核芯片组成的多处理器中,通常每个多核芯片都有独立的内存。因此,内存是分布式的,而不是集中式的。正如我们在本章后面将看到的,许多采用分布式内存的设计对本地内存的访问速度快,对远程内存的访问速度却要慢得多;通常,各个远程内存的访问时间差异相对于本地内存和远程内存的访问时间差异来说是微小的。在这种设计中,程序员和软件系统需要意识到访问是针对本地内存还是远程内存,但可能能够忽略远程内存之间访问的分布。

由于随着处理器数量的增加,SMP方法变得不那么有吸引力,因此大多数大型多处理器使用某种形式的分布式内存。

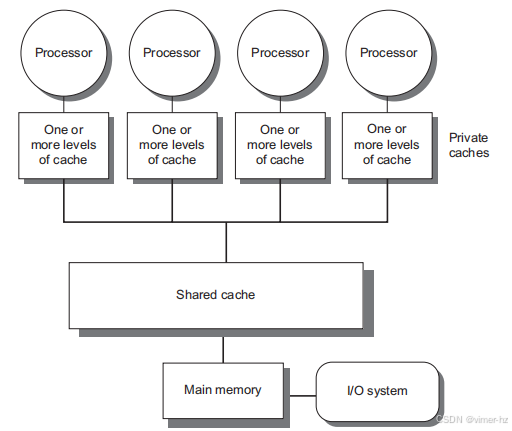

SMP架构有时也被称为统一内存访问(UMA)多处理器,这源于所有处理器从内存访问的延迟是统一的,即使内存被组织成多个银行。图5.1展示了这些多处理器的外观。SMP的架构是第5.2节的主题,我们将在多核背景下解释这一方法。

图5.1 基于多核芯片的集中式共享内存多处理器的基本结构。多个处理器缓存子系统共享同一物理内存,通常在多核上有一个级别的共享缓存,以及一个或多个级别的每核心私有缓存。关键的架构特性是所有处理器对所有内存的访问时间是统一的。在多芯片设计中,互连网络将处理器和可能是一个或多个内存银行的内存连接起来。在单芯片多核中,互连网络仅是内存总线。

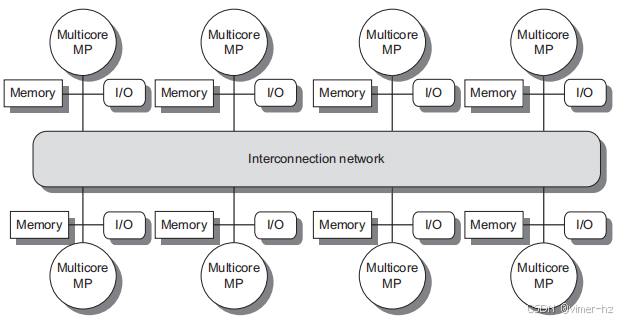

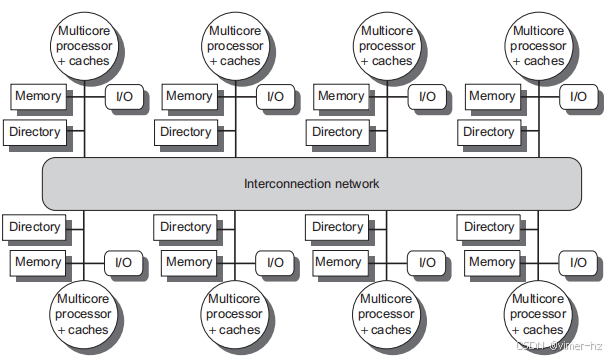

图5.2 2017年分布式内存多处理器的基本架构通常由一个多核多处理器芯片组成,该芯片附带内存和可能的I/O,以及一个与互连网络接口,连接所有节点。每个处理器核心共享整个内存,但连接到核心芯片的本地内存的访问时间将远快于对远程内存的访问时间。

另一种设计方法则是物理上分布式内存的多处理器,称为分布式共享内存(DSM)。图5.2展示了这些多处理器的外观。为了支持更多的处理器数量,内存必须在处理器之间分布,而不是集中;否则,内存系统将无法在不产生过长访问延迟的情况下支持更多处理器的带宽需求。

随着处理器性能的快速提升以及处理器内存带宽需求的增加,偏好使用分布式内存的多处理器规模不断缩小。多核处理器的引入意味着,即使是一些由2个芯片组成的多处理器(可能具有16到64个处理器核心)也采用分布式内存。处理器数量的增加也提升了对高带宽互连的需求,我们将在附录F中看到相关示例。无论是有向网络(即交换机)还是间接网络(通常为多维网状结构)都被广泛使用。

将内存分布在各个节点之间不仅增加了带宽,还减少了对本地内存的延迟。分布式共享内存(DSM)多处理器也被称为非统一内存访问(NUMA),因为访问时间取决于数据字在内存中的位置。DSM的主要缺点是处理器之间的数据通信变得稍微复杂,并且DSM需要更多的软件工作来利用分布式内存提供的增加内存带宽。由于大多数基于多核的多处理器系统使用分布式内存,因此我们将从这个角度解释分布式内存多处理器的操作。

在对称多处理(SMP)和分布式共享内存(DSM)架构中,线程之间的通信通过共享地址空间进行,这意味着任何处理器都可以引用任何内存位置,只要它拥有正确的访问权限。与SMP和DSM相关的共享内存术语指的是地址空间是共享的。

相比之下,下一章中的集群和大规模计算机看起来像是通过网络连接的独立计算机,一个处理器的内存无法在没有运行在两个处理器上的软件协议的帮助下被另一个处理器访问。在这样的设计中,使用消息传递协议在处理器之间传输数据。

### 并行处理的挑战

多处理器的应用范围从几乎没有通信的独立任务到需要线程间通信以完成任务的并行程序。两个重要的障碍可以用阿姆达尔法则来解释,这使得并行处理变得具有挑战性。克服这些障碍通常需要一个全面的方法,涉及算法及其实现、底层编程语言和系统、操作系统及其支持功能,以及架构和硬件实现。尽管在许多情况下,其中一个因素是关键瓶颈,但当处理器数量扩展到接近100个或更多时,往往所有软件和硬件的各个方面都需要关注。

第一个障碍与程序中可用的有限并行性有关,第二个障碍则源于通信的相对高成本。可用并行性的限制使得在任何并行处理器上取得良好的加速变得困难,正如我们的第一个例子所示。

**例子** 假设您想在100个处理器上实现80倍的加速。那么,原始计算中可以是顺序的部分占多少比例?

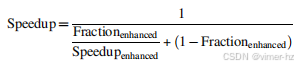

**答案** 回忆一下第一章,阿姆达尔法则是:

为了简化这个例子,假设程序仅在两种模式下运行:并行模式(所有处理器完全使用,即增强模式)和串行模式(仅使用一个处理器)。在这种简化情况下,增强模式下的加速简单地等于处理器的数量,而增强模式的比例则是花费在并行模式上的时间。将其代入前面的公式:

因此,要在100个处理器上实现80倍的加速,原始计算中只能有0.25%的部分是顺序的!当然,要实现线性加速(即用n个处理器获得n倍的加速),通常整个程序必须是并行的,没有任何串行部分。在实际应用中,程序并非仅在完全并行或串行模式下运行,而是在并行模式下通常使用的处理器数量少于全部处理器。阿姆达尔法则可以用来分析具有不同加速效果的应用,正如下一个例子所示。

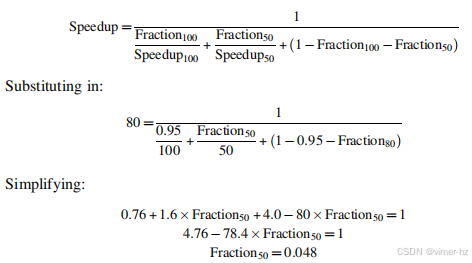

**例子** 假设我们有一个在100个处理器的多处理器上运行的应用程序,并且假设该应用程序可以使用1、50或100个处理器。如果我们假设在95%的时间内可以使用所有100个处理器,那么在剩余的5%执行时间中,必须使用多少个处理器才能实现80倍的加速?

**答案** 我们使用阿姆达尔法则,考虑更多的项:

如果一个应用程序95%的部分可以完美地使用100个处理器,要实现80倍的加速,剩余时间中必须有4.8%用于使用50个处理器,而仅有0.2%的时间可以是串行的!

并行处理中的第二个主要挑战涉及远程访问的高延迟。在现有的共享内存多处理器中,数据在不同核心之间的通信可能需要35到50个时钟周期,而在不同芯片上的核心之间则可能需要从100个时钟周期到300个或更多的时钟周期(对于大规模多处理器),这取决于通信机制、互连网络的类型和多处理器的规模。长时间的通信延迟显然会产生显著影响。让我们考虑一个简单的例子。

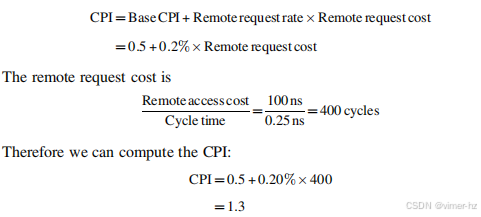

**例子** 假设我们有一个在32个处理器的多处理器上运行的应用程序,该应用程序处理对远程内存的引用时有100纳秒的延迟。对于该应用程序,假设除了涉及通信的引用外,所有引用都命中本地内存层级,这显然是乐观的。处理器在远程请求上会被阻塞,处理器的时钟频率为4 GHz。如果基准CPI(假设所有引用都在缓存中命中)为0.5,那么如果没有通信,与0.2%的指令涉及远程通信引用相比,多处理器的性能提升多少?

**答案** 首先计算每条指令的时钟周期会更简单。对于具有0.2%远程引用的多处理器,其有效CPI为:

多处理器在所有本地引用的情况下比基准快1.3/0.5,即2.6倍。实际上,性能分析要复杂得多,因为一部分非通信引用会在本地层级中未命中,而远程访问时间也不是一个固定的常数。例如,远程引用的成本可能会更高,因为多个引用试图使用全局互连造成的竞争可能导致延迟增加,或者如果内存是分布式的并且访问的是本地内存,则访问时间可能会更好。这个问题也可以使用阿姆达尔定律进行分析,我们将这一练习留给读者。

这些问题——不足的并行性和长延迟的远程通信——是使用多处理器时面临的两个最大性能挑战。必须主要通过软件解决应用程序并行性不足的问题,采用提供更好并行性能的新算法,以及通过最大化使用完整处理器组执行的时间的软件系统来解决。减少长远程延迟的影响可以通过架构和程序员两方面来解决。例如,我们可以通过硬件机制(如缓存共享数据)或软件机制(如重构数据以使更多访问变为本地访问)来降低远程访问的频率。我们还可以通过使用多线程(本章后面讨论)或预取(我们在第2章中广泛覆盖的主题)来尝试容忍延迟。

本章的大部分内容集中在减少长远程通信延迟影响的技术上。例如,第5.2至5.4节讨论了如何利用缓存来减少远程访问频率,同时保持内存的一致视图。第5.5节讨论了同步问题,这因为它固有地涉及处理器间通信,并且可能限制并行性,因此是一个主要的潜在瓶颈。第5.6节涵盖了延迟隐藏技术和共享内存的一致性模型。在附录I中,我们主要关注用于科学工作的较大规模多处理器。在该附录中,我们研究了这类应用的性质以及在几十到几百个处理器上实现加速的挑战。

5.2 Centralized Shared-Memory Architectures

使用大型多级缓存可以显著减少处理器的内存带宽需求,这一观察是驱动集中式内存多处理器发展的关键洞见。最初,这些处理器都是单核的,通常占据整个电路板,内存则位于共享总线上。随着最近更高性能处理器的出现,内存需求超出了合理总线的能力,现代微处理器直接将内存连接到单个芯片上,这有时被称为背面或内存总线,以区别于用于连接I/O的总线。访问芯片的本地内存,无论是针对I/O操作还是来自其他芯片的访问,都需要经过“拥有”该内存的芯片。因此,内存访问是不对称的:对本地内存的访问更快,而对远程内存的访问则较慢。在多核处理器中,这些内存在单个芯片上的所有核心之间共享,但从一个多核处理器访问另一个多核处理器的内存时,通常仍然存在这种不对称的情况。

对称共享内存机器通常支持共享数据和私有数据的缓存。私有数据由单个处理器使用,而共享数据则被多个处理器使用,本质上通过读取和写入共享数据提供了处理器之间的通信。当私有项被缓存时,其位置会迁移到缓存中,从而减少平均访问时间以及所需的内存带宽。由于没有其他处理器使用该数据,因此程序行为与单处理器中的行为相同。当共享数据被缓存时,共享值可能会在多个缓存中复制。除了减少访问延迟和所需内存带宽外,这种复制还减少了可能因多个处理器同时读取共享数据项目而产生的竞争。然而,共享数据的缓存引入了一个新问题:缓存一致性。

### 什么是多处理器缓存一致性?

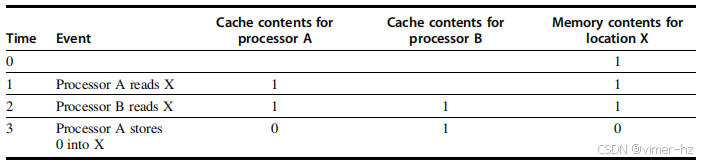

不幸的是,缓存共享数据引入了一个新问题。由于两个不同处理器对内存的视图是通过各自的缓存实现的,这些处理器可能会看到同一内存位置的不同值,如图5.3所示。这种困难通常被称为缓存一致性问题。注意,一致性问题的存在是因为我们同时拥有一个主要由主内存定义的全局状态和一个由每个处理器核心私有的各自缓存定义的局部状态。因此,在某个级别的缓存可能是共享的多核系统中(例如,L3),尽管某些级别是私有的(例如,L1和L2),一致性问题仍然存在并且必须解决。

图5.3 单个内存位置(X)的缓存一致性问题,由两个处理器(A和B)进行读写。我们最初假设两个缓存均不包含该变量,并且X的值为1。我们还假设使用的是直写缓存;而写回缓存则会增加一些额外但类似的复杂性。在A写入X的值后,A的缓存和内存都包含新值,但B的缓存不包含该值,如果B读取X的值,它将接收到1!

非正式地说,如果任何对数据项的读取返回该数据项最近写入的值,我们可以称内存系统是一致的。这个定义虽然在直观上很吸引人,但却模糊而简单;现实情况要复杂得多。这个简单的定义包含内存系统行为的两个不同方面,这两个方面对于编写正确的共享内存程序都是至关重要的。第一个方面称为一致性,定义了读取时可以返回哪些值;第二个方面称为一致性性,决定了何时会通过读取返回已写入的值。让我们先看一致性。

如果一个内存系统是一致的,则满足以下条件:

1. 处理器P在对位置X进行写操作后,随后对X进行读取时,如果在P的写操作和读取之间没有其他处理器对X进行写操作,则总是返回P写入的值。

2. 处理器对位置X的读取跟随另一个处理器对X的写入时,如果读取与写入在时间上有足够的间隔,并且在这两个访问之间没有对X的其他写入,则返回已写入的值。

3. 对同一位置的写入是串行化的;即,任何两个处理器对同一位置的两个写入在所有处理器中以相同的顺序被看到。

例如,如果值1然后值2被写入某个位置,处理器不能读到该位置的值为2,然后再读为1。第一个属性简单地保持程序顺序——我们期望即使在单处理器中这个属性也为真。第二个属性定义了何为一致的内存视图:如果一个处理器能够持续读取旧的数据值,我们显然会说内存是不一致的。

写入序列化的需求更为微妙,但同样重要。假设我们没有对写操作进行序列化,处理器P1先写入位置X,随后P2也写入位置X。序列化写入确保每个处理器都能在某个时间点看到P2的写入。如果不进行序列化,可能会出现某些处理器先看到P2的写入,然后再看到P1的写入,从而无限期地保持P1写入的值。避免这种困难的最简单方法是确保对同一位置的所有写入以相同的顺序被看到;这个特性称为写入序列化。

虽然刚刚描述的三个属性足以确保一致性,但何时能看到已写入值的问题也很重要。要理解这一点,注意我们不能要求读取X时立即看到由其他处理器写入的值。例如,如果一个处理器对X的写入在另一个处理器读取X之前只相差很短的时间,那么可能无法确保该读取返回写入的数据值,因为该数据甚至可能尚未离开处理器。读取器必须在何时看到已写入值的问题由内存一致性模型定义——这一主题将在第5.6节中讨论。

一致性和连贯性是互补的:连贯性定义了对同一内存位置的读取和写入的行为,而一致性则定义了对其他内存位置的读取和写入的行为。现在,我们做以下两个假设。首先,一个写入在所有处理器看到该写入的效果之前不会完成(并允许下一个写入发生)。其次,处理器不会改变任何写入与其他内存访问的顺序。这两个条件意味着,如果一个处理器先写入位置A,再写入位置B,则任何看到B的新值的处理器也必须看到A的新值。这些限制允许处理器重新排序读取,但强制处理器按照程序顺序完成写入。我们将依赖这个假设,直到第5.6节,在那里我们将看到这一定义的确切含义以及替代方案。

### 强化一致性的基本方案

对于多处理器和I/O的一致性问题,尽管源头相似,但由于其特性不同,因此适当的解决方案也有所不同。与I/O不同,后者多个数据副本是一种少见的事件——应尽量避免——而在多个处理器上运行的程序通常会在多个缓存中存在相同数据的副本。在一致性多处理器中,缓存提供了共享数据项的迁移和复制功能。

一致性缓存提供迁移,因为数据项可以被移动到本地缓存中,并以透明的方式使用。这种迁移减少了访问远程分配的共享数据项的延迟,以及对共享内存带宽的需求。

由于缓存会在本地缓存中复制数据项,一致性缓存还为同时读取的共享数据提供了复制功能。复制减少了访问延迟和对读取共享数据项的争用。支持这种迁移和复制对访问共享数据的性能至关重要。因此,多处理器并不试图通过软件避免这个问题,而是通过引入协议来维护一致性缓存,从而采用硬件解决方案。

维护多个处理器一致性的协议称为缓存一致性协议。实现缓存一致性协议的关键是跟踪任何数据块共享的状态。缓存块的状态通过与块关联的状态位来保持,这类似于单处理器缓存中的有效位和脏位。当前使用的协议可分为两类,每种类使用不同的技术来跟踪共享状态:

- **基于目录的协议**——特定物理内存块的共享状态保存在一个位置,称为目录。基于目录的缓存一致性有两种非常不同的类型。在对称多处理器(SMP)中,可以使用一个集中式目录,该目录与内存或其他单一的序列化点(例如,多核中的最外层缓存)相关联。在分布式共享内存(DSM)中,拥有一个单一目录是没有意义的,因为这会造成单点争用,并使得在多核心芯片的内存需求下难以扩展。分布式目录比单一目录更复杂,这种设计在第5.4节中讨论。

- **监听协议**——而不是将共享状态保存在单一目录中,每个拥有物理内存块数据副本的缓存可以跟踪该块的共享状态。在SMP中,缓存通常通过某种广播介质(例如,总线将每个核心的缓存连接到共享缓存或内存)可供访问,所有缓存控制器监控或监听该介质,以确定它们是否拥有总线或交换访问请求的块的副本。监听协议也可以作为多芯片多处理器的协调协议,一些设计支持在每个多核内的目录协议之上使用监听协议。

监听协议在使用微处理器(单核心)和通过总线连接到单个共享内存的缓存的多处理器中变得流行。总线提供了一个方便的广播介质来实现监听协议。多核架构显著改变了这一局面,因为所有多核都共享芯片上的某些级别的缓存。因此,一些设计转向使用目录协议,因为其开销较小。为了让读者熟悉这两种类型的协议,我们在这里重点介绍监听协议,并在讨论DSM架构时讨论目录协议。

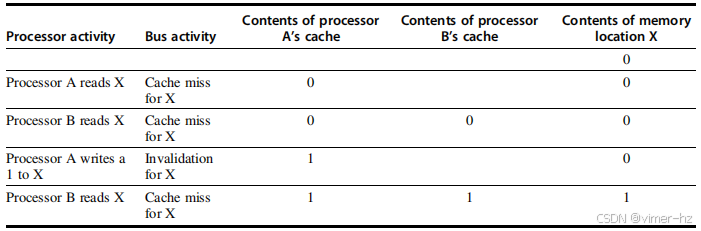

### 监听一致性协议

有两种方法来维持前一节中描述的一致性要求。一种方法是在写入数据项之前,确保处理器对该数据项具有独占访问权限。这种协议被称为写入失效协议,因为在写入时会使其他副本失效。这是迄今为止最常见的协议。独占访问确保在写入发生时不存在其他可读或可写的副本:所有其他缓存的副本都会被失效。

图5.4 一个在窥探总线上工作的失效协议示例,涉及单个缓存块(X)和写回缓存。我们假设初始时没有任何缓存持有X,并且内存中X的值为0。在处理器和总线活动完成后,处理器和内存的内容显示了相应的值。空白表示没有活动或没有缓存副本。当处理器B发生第二次未命中时,处理器A用值响应,取消了来自内存的响应。此外,B的缓存内容和内存中X的内容都会被更新。这种在块变为共享时更新内存的方式简化了协议,但也可以跟踪所有权并强制写回,仅在块被替换时才进行。这需要引入一个额外的状态位,以指示块的所有权。所有权位表示一个块可能被共享用于读取,但只有拥有该块的处理器可以写入该块,而该处理器负责在更改或替换块时更新其他处理器和内存。如果多核使用共享缓存(例如L3),那么所有内存都通过共享缓存进行访问;在这个例子中,L3充当内存,且必须处理每个核心私有的L1和L2缓存的一致性。正是这一观察促使一些设计者选择在多核系统中采用目录协议。为了使其有效,L3缓存必须是包含性的;回想一下第2章,一种缓存是包含性的,如果较高层级缓存(在此情况下为L1和L2)中的任何位置也在L3中。我们将在423页回到包含性主题。

图5.4展示了一个带有写回缓存的失效协议的示例。为了理解该协议如何确保一致性,可以考虑一个处理器的写操作后,另一个处理器的读操作:由于写入需要独占访问,任何由读取处理器持有的副本必须失效(因此得名)。因此,当读取发生时,它会在缓存中未命中,必须强制获取数据的新副本。对于写操作,我们要求写入处理器具有独占访问权限,防止任何其他处理器能够同时写入。如果两个处理器确实尝试同时写入相同的数据,其中一个会赢得竞争(我们稍后会看到如何决定谁胜出),导致另一个处理器的副本失效。为了完成写入,另一个处理器必须获取数据的新副本,而此副本现在必须包含更新的值。由此可见,该协议强制执行写入序列化。

与失效协议的替代方案是在写入数据项时更新所有缓存的副本。这种类型的协议被称为写入更新或写入广播协议。由于写入更新协议必须将所有写入广播到共享缓存行,因此它消耗的带宽显著更多。因此,几乎所有近期的多处理器都选择实现写入失效协议,我们将在本章剩余部分专注于失效协议。

### 基本实现技术

在多核系统中实施失效协议的关键是利用总线或其他广播媒介来执行失效操作。在较早的多芯片多处理器中,用于保持一致性的总线是共享内存访问总线。在单芯片多核中,总线可以是私有缓存(如Intel i7中的L1和L2)与共享外部缓存(如i7中的L3)之间的连接。要执行失效操作,处理器只需获得总线访问权限,并在总线上广播要失效的地址。所有处理器会持续监听总线,观察地址。如果总线上的地址在它们的缓存中存在,则相应的数据会被标记为无效。

当对共享块进行写操作时,写入处理器必须获得总线访问权限以广播其失效。在两个处理器尝试同时写入共享块时,它们在争用总线时将会序列化其失效操作。第一个获得总线访问权限的处理器会使它正在写入的块的其他副本失效。如果处理器尝试写入同一个块,总线强制的序列化也将序列化它们的写入。这种方案的一个含义是,对共享数据项的写入在获得总线访问之前实际上无法完成。所有一致性方案都需要某种方法来序列化对同一缓存块的访问,或者通过序列化对通信媒介的访问,或对其他共享结构的访问。

除了使正在写入的缓存块的未决副本失效外,我们还需要在发生缓存未命中的时候找到数据项。在直写缓存中,查找数据项的最新值很简单,因为所有写入的数据始终会发送到内存,从中可以始终获取数据项的最新值。(写缓冲区可能导致一些额外的复杂性,必须有效地视为额外的缓存条目。)

对于写回缓存,查找最新数据值的问题更为复杂,因为数据项的最新值可能在私有缓存中,而不是在共享缓存或内存中。幸运的是,写回缓存可以对缓存未命中和写入使用相同的监听机制:每个处理器监听所有放置在共享总线上的地址。如果某个处理器发现它有请求的缓存块的脏副本,它会在响应读取请求时提供该缓存块,并使内存(或L3)访问被中止。额外的复杂性来自于需要从另一个处理器的私有缓存(L1或L2)中检索缓存块,这通常比从L3中检索要花费更长的时间。由于写回缓存对内存带宽的要求较低,因此可以支持更多数量的更快处理器。因此,所有多核处理器在缓存的最外层级别上都使用写回缓存,我们将研究带有写回缓存的一致性实现。

正常的缓存标签可以用于实现监听过程,每个块的有效位使得失效操作的实现变得简单。读取未命中,无论是由于失效还是其他事件引起的,都很直接,因为它们仅依赖于监听能力。对于写入,我们希望知道该块是否有其他副本被缓存,因为如果没有其他缓存副本,则在写回缓存中写入不需要放置在总线上。不发送写入可以减少写入时间和所需带宽。

为了跟踪缓存块是否共享,我们可以为每个缓存块添加一个额外的状态位,就像我们有有效位和脏位一样。通过添加一个指示块是否共享的位,我们可以决定写入是否必须生成失效。当对处于共享状态的块进行写入时,缓存会在总线上生成失效并将该块标记为独占。此后,该核心不会再对该块发送进一步的失效请求。拥有缓存块唯一副本的核心通常被称为该缓存块的所有者。

当发送失效时,所有者的缓存块状态会从共享变为非共享(或独占)。如果另一个处理器随后请求这个缓存块,状态必须再次变为共享。由于我们的监听缓存也能看到任何未命中,它会知道独占缓存块何时被另一个处理器请求,从而将状态更改为共享。

每个总线事务必须检查缓存地址标签,这可能会干扰处理器的缓存访问。减少这种干扰的一种方法是复制标签,并将监听访问指向复制的标签。另一种方法是在共享的L3缓存中使用目录;该目录指示给定块是否共享,以及可能哪些核心有副本。通过目录信息,可以仅将失效请求定向到那些有缓存块副本的缓存。这要求L3始终必须有L1或L2中任何数据项的副本,这一特性称为包含性,我们将在第5.7节中回到这一点。

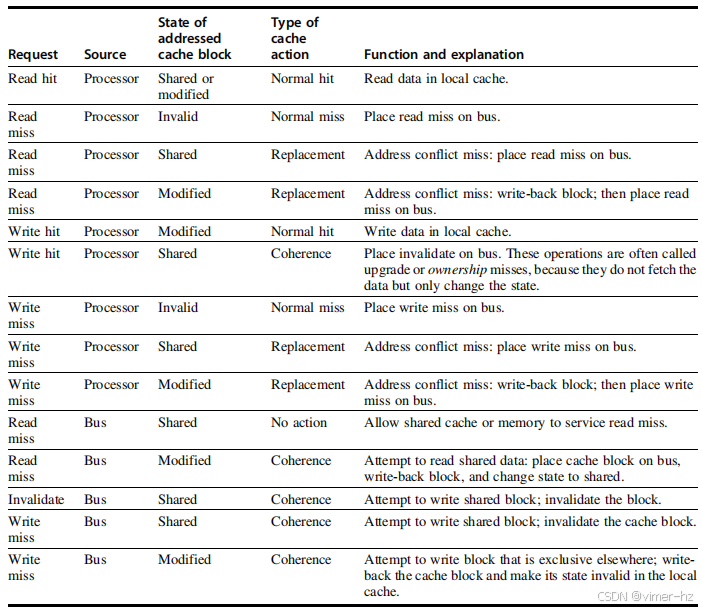

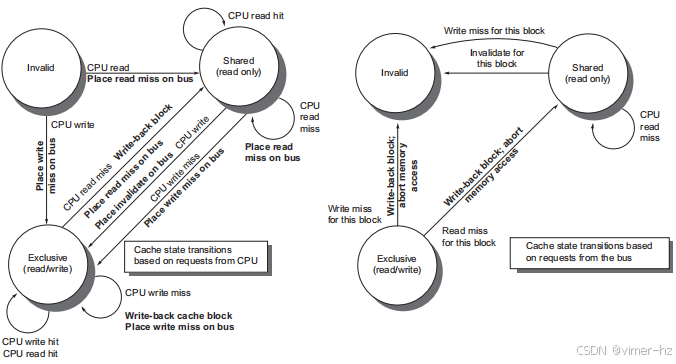

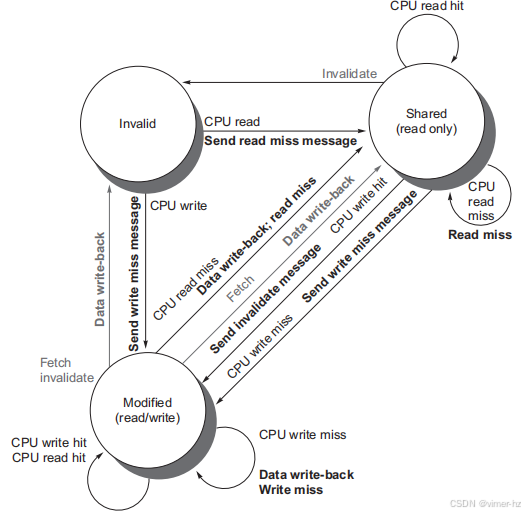

### 示例协议

窥探一致性协议通常通过在每个核心中集成一个有限状态控制器来实现。该控制器响应来自核心处理器和总线(或其他广播媒介)的请求,改变所选缓存块的状态,并利用总线访问数据或使其失效。逻辑上,可以将每个块视为有一个独立的控制器;也就是说,不同块的窥探操作或缓存请求可以独立进行。在实际实现中,单个控制器允许多个对不同块的操作以交错的方式进行(即,一个操作可以在另一个操作完成之前启动,尽管同一时间只能允许一次缓存访问或一次总线访问)。此外,请记住,尽管我们在以下描述中提到总线,但任何支持广播到所有一致性控制器及其相关私有缓存的互连网络都可以用于实现窥探。

图5.5 缓存一致性机制接收来自核心处理器和共享总线的请求,并根据请求的类型、在本地缓存中是否命中或缺失,以及请求中指定的本地缓存块的状态作出响应。第四列描述了缓存操作的类型,包括正常命中或缺失(与单处理器缓存相同)、替换(单处理器缓存替换缺失)或一致性(用于维持缓存一致性);正常或替换操作可能会引发一致性操作,具体取决于其他缓存中块的状态。对于从总线上窥探到的读取缺失、写入缺失或使失效的请求,仅当读取或写入地址与本地缓存中的某个块匹配且该块有效时,才需要采取相应的操作。

我们考虑的简单协议有三个状态:无效、共享和修改。共享状态表示私有缓存中的块可能是共享的,而修改状态表示该块在私有缓存中已被更新;需要注意的是,修改状态意味着该块是独占的。图5.5显示了核心生成的请求(表格的上半部分)以及来自总线的请求(表格的下半部分)。该协议适用于写回缓存,但通过将修改状态重新解释为独占状态,并按照写透缓存的正常方式在写入时更新缓存,可以轻松更改为写透缓存。该基本协议最常见的扩展是添加一个独占状态,描述一个未修改但仅保存在一个私有缓存中的块。我们将在第388页描述这个和其他扩展。

当无效化或写入缺失请求被放置在总线上时,任何拥有该缓存块副本的私有缓存的核心都会使其失效。对于写回缓存中的写入缺失,如果该块仅在一个私有缓存中是独占的,那么该缓存也会将该块写回;否则,数据可以从共享缓存或内存中读取。

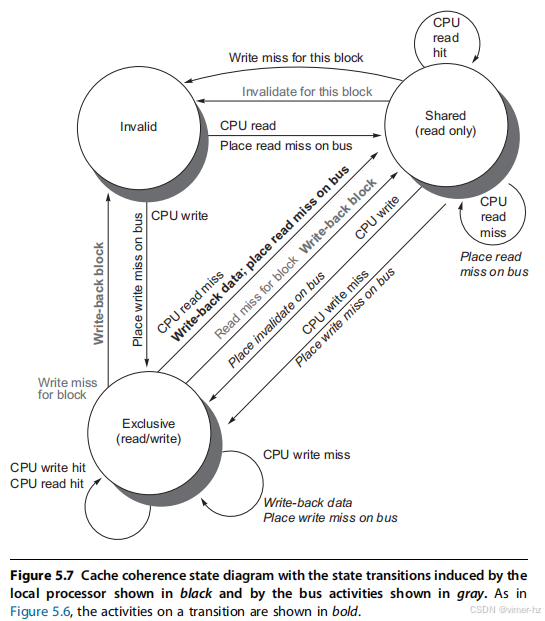

图5.6 显示了一个用于私有写回缓存的写无效化缓存一致性协议,展示了缓存中每个块的状态和状态转换。缓存状态以圆圈表示,任何本地处理器在不发生状态转换的情况下允许的访问以括号形式显示在状态名称下。导致状态变化的刺激在转移弧线上用常规字体显示,而作为状态转换一部分生成的总线操作则用粗体显示。刺激行为适用于私有缓存中的一个块,而不是缓存中的特定地址。因此,对共享状态块的读取缺失对于该缓存块来说是缺失,但涉及的是不同的地址。图的左侧显示了基于与该缓存相关联的处理器操作的状态转换;右侧则显示基于总线操作的转换。当处理器请求的地址与本地缓存块中的地址不匹配时,在独占状态或共享状态下发生读取缺失和在独占状态下的写入缺失。这种缺失是标准的缓存替换缺失。尝试写入共享状态的块会产生无效化。每当发生总线事务时,所有包含总线事务中指定的缓存块的私有缓存都会采取图右侧规定的行动。该协议假设内存(或共享缓存)在读取缺失时提供干净块的数据信息。在实际实现中,这两组状态图是结合在一起的。在实践中,关于无效化协议存在许多微妙的变体,包括引入独占未修改状态,以及处理器或内存在缺失时提供数据的情况。在多核芯片中,共享缓存(通常是L3,有时是L2)相当于内存,而总线则是各核心私有缓存与共享缓存之间的总线,后者又与内存接口。

图5.6展示了使用写无效化协议和写回缓存的单个私有缓存块的有限状态转换图。为简化起见,协议的三个状态被复制,以表示基于处理器请求的转换(左侧,对应于图5.5上半部分的表格),与基于总线请求的转换(右侧,对应于图5.5下半部分的表格)相区分。加粗字体用于区分总线操作,而不是依赖于状态转换的条件。每个节点中的状态表示由处理器或总线请求指定的选定私有缓存块的状态。

在单处理器缓存中,所有这些状态都是必要的,它们对应于无效、有效(干净)和脏状态。图5.6左半部分中通过弧线表示的大多数状态变化在写回单处理器缓存中都是需要的,唯一的例外是对共享块的写命中的无效化。图5.6右半部分中通过弧线表示的状态变化仅用于一致性,并且在单处理器缓存控制器中不会出现。

如前所述,每个缓存只有一个有限状态机,其刺激来自附加的处理器或总线。图5.7展示了图5.6右半部分中的状态转换如何与左半部分中的状态转换结合,以形成每个缓存块的单一状态图。

为了理解这个协议为何有效,需要注意到任何有效的缓存块要么在一个或多个私有缓存中处于共享状态,要么在恰好一个缓存中处于独占状态。任何转变为独占状态(这对于处理器写入该块是必要的)都需要在总线上放置无效化或写缺失信号,导致所有本地缓存将该块标记为无效。此外,如果其他某个本地缓存中的块处于独占状态,该本地缓存会生成写回操作,从而提供包含所需地址的块。最后,如果在总线上对一个处于独占状态的块发生读取缺失,拥有独占副本的本地缓存会将其状态更改为共享。

图5.7中灰色部分的操作处理了总线上的读写缺失,这本质上是该协议的监听组件。该协议及大多数其他协议保持的另一个属性是,任何处于共享状态的内存块在外部共享缓存(L2或L3,或者如果没有共享缓存则是内存)中始终是最新的,这简化了实现。实际上,从私有缓存出来的层级是共享缓存还是内存并不重要;关键在于所有来自核心的访问都通过这一层级。

尽管我们的简单缓存协议是正确的,但它省略了一些使实现更加复杂的细节。其中最重要的是,该协议假设操作是原子的——即,操作可以以一种方式执行,使得没有其他干预操作可以发生。例如,所描述的协议假设可以检测到写缺失、获得总线并作为单一原子操作接收响应。实际上,这并不是事实。实际上,甚至读取缺失也可能不是原子的;在多核系统中,核心在L2中检测到缺失后,必须争夺连接到共享L3的总线访问权。非原子操作引入了协议可能死锁的可能性,这意味着它达到了无法继续的状态。我们将在本节稍后探讨这些复杂性,并在研究分布式共享内存设计时进一步讨论。

随着多核处理器的发展,处理器核心之间的缓存一致性都是在芯片上实现的,通常使用监听协议或简单的中央目录协议。许多多处理器芯片,包括英特尔的Xeon和AMD的Opteron,支持通过连接芯片中已有的高速接口构建的多芯片多处理器。这些更高级别的互连不仅仅是共享总线的扩展,而是采用不同的方法来互连多核处理器。由多个多核芯片构建的多处理器通常具有分布式内存架构,并需要一种在芯片之外的芯片间一致性机制。在大多数情况下,都会使用某种形式的目录方案。

### 基本一致性协议的扩展

我们刚刚描述的一致性协议是一个简单的三状态协议,通常用状态的首字母来称呼,因此称为MSI(修改、共享、无效)协议。这个基本协议有许多扩展,我们将在本节图形的说明中提到。这些扩展通过添加额外的状态和事务来优化某些行为,从而可能提高性能。最常见的两种扩展是:

1. **MESI**:在基本的MSI协议中添加了“独占”状态,形成四种状态(修改、独占、共享和无效)。独占状态表示缓存块仅存在于单个缓存中并且是干净的。如果某个块处于E状态,可以在不生成任何无效通知的情况下写入,这优化了在单个缓存中读取后再写入同一缓存的情况。当然,当对E状态的块发生读取未命中时,该块必须转换为S状态以维持一致性。由于所有后续访问都被监听,能够保持该状态的准确性。特别是,如果另一个处理器发出读取未命中请求,状态会从独占变为共享。添加此状态的优势在于,同一核心对独占状态的块后续写入无需获取总线访问权限或生成无效通知,因为该块已知仅在本地缓存中;处理器只需将状态更改为修改。这个状态可以通过将编码一致性状态的位用作独占状态,并使用脏位指示块已被修改来轻松添加。英特尔i7使用了一种MESI协议的变体,称为MESIF,增加了一个状态(转发),用于指定哪个共享处理器应响应请求。该设计旨在提高分布式内存组织中的性能。

2. **MOESI**:在MESI协议中添加了“拥有”状态,以指示相关块由该缓存拥有且主存中已过期。在MSI和MESI协议中,当尝试共享处于修改状态的块时,状态会变为共享(在原始缓存和新共享缓存中均如此),并且该块必须写回内存。在MOESI协议中,可以在原始缓存中将块从修改状态更改为拥有状态,而无需写入内存。其他新共享该块的缓存保持块处于共享状态;只有原始缓存持有的O状态表示主存中的副本已过期,并且指定的缓存是所有者。块的所有者在发生未命中时必须提供该块,因为内存未更新,并且如果被替换则必须将该块写回内存。AMD Opteron处理器系列使用MOESI协议。

下一部分将考察这些协议在我们的并行和多程序工作负载中的性能;当我们检查性能时,这些扩展对基本协议的价值将会显而易见。但在此之前,让我们简要看看对使用对称内存结构和监听一致性方案的限制。

### 对称共享内存多处理器和监听协议的局限性

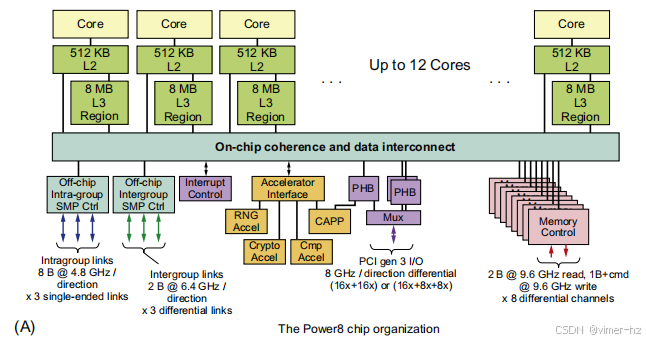

随着多处理器中处理器数量的增加,或各处理器对内存的需求增长,系统中的任何集中资源都可能成为瓶颈。在多核系统中,即使只有少数核心,单一的共享总线也会成为瓶颈。因此,多核设计采用了更高带宽的互连方案,以及多个独立的内存,以支持更多核心。我们在第5.8节中审查的多核芯片使用了三种不同的方法:

1. **IBM Power8**:在单个多核中最多可以容纳12个处理器,使用8条并行总线连接分布式L3缓存和最多8个独立内存通道。

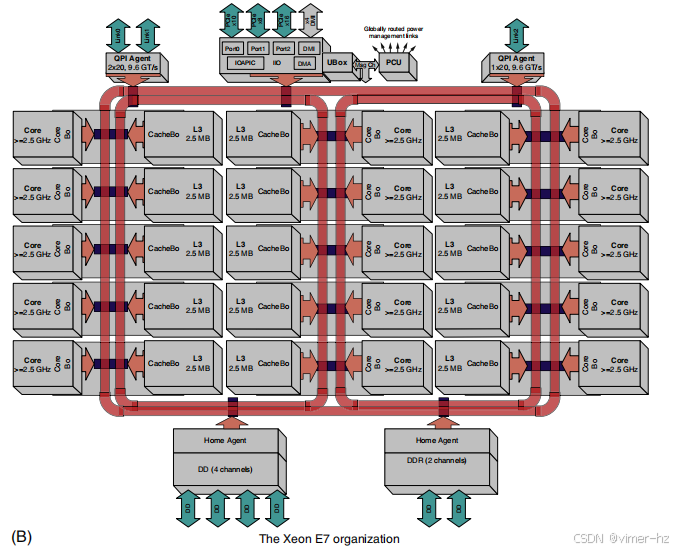

2. **Xeon E7**:使用三条环路连接最多32个处理器、一个分布式L3缓存以及两个或四个内存通道(具体取决于配置)。

3. **Fujitsu SPARC64 X+**:使用交叉开关将共享L2连接到最多16个核心和多个内存通道。

SPARC64 X+是一个对称组织,具有统一的访问时间。Power8则在L3和内存方面具有非统一的访问时间。尽管在单个Power8多核内,不同内存地址之间的无争用访问时间差异并不大,但在内存存在争用时,即便是在同一芯片内,这些访问时间差异可能变得显著。Xeon E7可以像访问时间统一一样运行;在实践中,软件系统通常会将内存组织为与部分核心相关联的内存通道。

缓存中的监听带宽也可能成为问题,因为每个缓存必须检查每一次未命中,而额外的互连带宽只能将问题转移到缓存。为了理解这个问题,可以考虑以下示例。

### 示例

考虑一个8处理器的多核系统,其中每个处理器都有自己的L1和L2缓存,并且在L2缓存之间通过共享总线进行监听。假设平均L2请求,无论是由于一致性未命中还是其他未命中,都是15个时钟周期。假设时钟频率为3.0 GHz,CPI(每指令周期)为0.7,加载/存储频率为40%。

如果我们的目标是确保一致性流量不超过L2带宽的50%,那么每个处理器的最大一致性未命中率是多少?

### 解答

首先,我们从可用缓存周期的方程开始(其中CMR为一致性未命中率):

这意味着一致性未命中率必须为0.73%或更低。在下一部分,我们将看到一些应用的一致性未命中率超过1%。另外,如果我们假设CMR可以达到1%,那么我们最多可以支持不到6个处理器。显然,即使是小型多核系统也需要一种方法来扩展监听带宽。

有几种技术可以增加监听带宽:

1. 正如前面提到的,标签可以进行重复。这将有效地将缓存级别的监听带宽翻倍。如果我们假设一半的一致性请求在监听请求上没有命中,并且监听请求的成本只有10个周期(与15个周期相比),那么我们可以将CMR的平均成本降低到12.5个周期。这一减少允许一致性未命中率达到0.88,或者支持一个额外的处理器(7个与6个相比)。

2. 如果多核系统中最外层的缓存(通常是L3)是共享的,我们可以将该缓存分配给每个处理器,使每个处理器拥有一部分内存并处理该地址空间部分的监听请求。这种方法被IBM 12核Power8采用,导致了一种NUCA设计,但有效地根据处理器数量扩展L3的监听带宽。如果L3中出现监听命中,我们仍然必须向所有L2缓存广播,这些缓存又必须监听其内容。由于L3充当了监听请求的过滤器,因此L3必须是包含性的。

3. 我们可以在最外层共享缓存(例如L3)上放置一个目录。L3充当监听请求的过滤器,并且必须是包含性的。在L3使用目录意味着我们不必对所有L2缓存进行监听或广播,而只需对目录指示可能拥有块副本的缓存进行操作。正如L3可以被分布,相关的目录条目也可以分布。这种方法在支持8到32个核心的Intel Xeon E7系列中得到了应用。

图5.8 显示了一个具有分布式缓存的单芯片多核处理器。在当前设计中,分布式共享缓存通常是L3,而L1和L2级别是私有的。通常有多个内存通道(在今天的设计中为2到8个)。该设计是NUCA,因为访问L3各部分的时间因直接连接的核心而异,访问时间更快。由于它是NUCA,因此它也是NUMA。

图5.8展示了一个具有分布式缓存系统的多核处理器的示例,类似于方案2或方案3中使用的系统。如果要添加更多的多核芯片以形成更大的多处理器系统,则需要一个外部网络以及扩展一致性机制的方法(我们将在第5.8节中讨论)。

AMD Opteron代表了一种介于监听协议和目录协议之间的中间点。内存直接连接到每个多核芯片,并且最多可以连接四个多核芯片。该系统是NUMA,因为本地内存的速度相对较快。Opteron通过点对点链接实现其一致性协议,以广播到多达三个其他芯片。由于处理器间的链接不共享,因此处理器知道无效操作何时完成的唯一方式是通过显式确认。因此,一致性协议使用广播来查找潜在共享的副本,类似于监听协议,但使用确认来排序操作,就像目录协议一样。由于在Opteron实现中,本地内存的速度仅比远程内存稍快,一些软件将Opteron多处理器视为具有统一内存访问。

在第5.4节中,我们讨论了基于目录的协议,这种协议消除了在缺失时向所有缓存广播的需求。一些多核设计在多核内部使用目录(例如Intel Xeon E7),而另一些则在规模超出多核时添加目录。分布式目录消除了串行化所有访问的单一节点需求(通常是监听方案中的单一共享总线),任何去除单一串行化节点的方案都必须面对与分布式目录方案类似的许多挑战。

### 实现窥探缓存一致性

魔鬼藏在细节中。

——经典谚语

当我们在1990年撰写本书的第一版时,我们最终的“整合”是一个使用基于窥探一致性的30处理器单总线多处理器系统;该总线的带宽刚好超过50 MiB/s,这已不足以支持2017年一颗Intel i7核心的带宽!在1995年撰写本书第二版时,首批具有多个总线的缓存一致性多处理器刚刚出现,我们在附录中增加了描述在多个总线系统中实现窥探的方法。到2017年,所有支持8个或更多核心的多核多处理器系统都使用除了单总线之外的互连,设计人员必须面对在没有简化总线来串行化事件的情况下实施窥探(或目录方案)的挑战。

正如我们在第386页所观察到的,实际实现我们所描述的窥探一致性协议的主要复杂性在于,写入和升级失效在最近的多处理器中并不是原子的。检测写入或升级失效、与其他处理器和内存通信、获取写入失效的最新值、确保任何失效请求被处理以及更新缓存的步骤不能视为在单个周期内完成。

在具有单一总线的多核系统中,这些步骤可以通过首先争用共享缓存或内存的总线(在更改缓存状态之前)并且在所有操作完成之前不释放总线,从而有效地使这些步骤变得原子。处理器如何知道所有失效请求何时完成?在早期设计中,使用单一信号线来指示所有必要的失效请求已经接收并正在处理。收到该信号后,产生失效的处理器可以释放总线,知道任何所需的操作将在与下一个失效相关的活动之前完成。通过在这些步骤中独占总线,处理器有效地使各个步骤具有了原子性。

在没有单一中央总线的系统中,我们必须找到其他方法来使失效步骤具有原子性。特别是,我们必须确保两个处理器在同一时间尝试写入同一块数据,这种情况称为竞争,能够严格排序:一个写入被处理并在下一个写入开始之前完成。两个写入在竞争中哪一个获胜并不重要,只要有一个赢家,其一致性操作首先完成。在使用多个总线的多核系统中,如果每个内存块只与单一总线关联,则可以消除竞争,这样对同一块的两个访问请求必须通过该公共总线串行化。这一特性,以及在竞争中重新启动失败者的失效处理能力,是在没有总线的情况下实现窥探缓存一致性的关键。我们在附录I中解释了细节。

结合窥探和目录也是可能的,多个设计在多核内部使用窥探,并在多个芯片之间使用目录,或者在一个缓存层级使用目录,在另一个层级使用窥探的组合。

5.3 Performance of Symmetric Shared-Memory Multiprocessors

在使用窥探一致性协议的多核系统中,多个不同现象共同决定性能。特别是,整体缓存性能是单处理器缓存未命中流量行为与由通信引起的流量(导致失效和随后的缓存未命中)之间的结合。改变处理器数量、缓存大小和块大小会以不同方式影响这两个未命中率的组成部分,从而导致整体系统行为是这两种效应的组合。

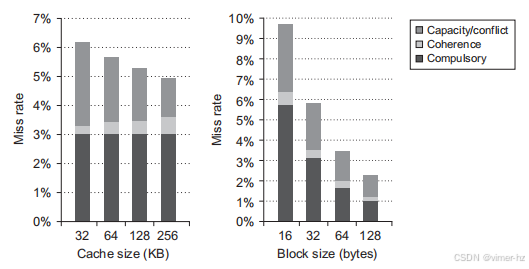

附录B将单处理器的未命中率分为三类(容量、强制和冲突),并提供了对应用行为和潜在缓存设计改进的洞察。同样,由于处理器之间的通信而产生的未命中,通常称为一致性未命中,可以分为两个独立的来源。

第一个来源是真共享未命中,这种未命中源于通过缓存一致性机制传递数据的通信。在基于失效的协议中,一个处理器对共享缓存块的第一次写入会导致失效,以确立该块的所有权。此外,当另一个处理器试图读取该缓存块中的修改字时,会发生未命中,并转移相应的块。这两种未命中都被归类为真共享未命中,因为它们直接源于处理器之间的数据共享。

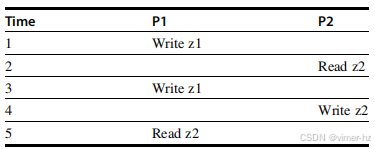

第二种效应称为假共享,它源于使用每个缓存块一个有效位的基于失效的一致性算法。当一个块被失效(而后续引用导致未命中)是因为块中除被读取的字之外的其他字被写入时,就会发生假共享。如果写入的字实际上被接收到失效的处理器使用,那么该引用就是一个真共享引用,并且将导致未命中,而不依赖于块大小。然而,如果被写入的字和被读取的字不同,并且失效没有导致新值的传递,而只是导致额外的缓存未命中,那么这就是假共享未命中。在假共享未命中中,块是共享的,但缓存中的字实际上并没有共享,如果块大小为一个字,则不会发生未命中。以下示例清楚地说明了共享模式。

例子 假设字 z1 和 z2 位于同一个缓存块中,该块在 P1 和 P2 的缓存中处于共享状态。根据以下事件序列,判断每个未命中是一个真共享未命中、假共享未命中还是命中。任何如果块大小为一个字而发生的未命中被指定为真共享未命中。

回答 下面是按时间步骤分类的结果:

1. 该事件是一个真共享未命中,因为 z1 在 P2 中处于共享状态,需要从 P2 中失效。

2. 该事件是一个假共享未命中,因为 z2 被 P1 中对 z1 的写操作失效,但 P2 并没有使用 z1 的值。

3. 该事件是一个假共享未命中,因为包含 z1 的块由于 P2 的读取而标记为共享,但 P2 并没有读取 z1。在 P2 读取后,包含 z1 的缓存块将处于共享状态;需要一个写未命中以获得对该块的独占访问。在某些协议中,这将被视为升级请求,生成一个总线失效,但不会传输缓存块。

4. 该事件是一个假共享未命中,原因与第 3 步相同。

5. 该事件是一个真共享未命中,因为读取的值是由 P2 写入的。尽管我们将在商业工作负载中看到真共享和假共享未命中的影响,但对于共享大量用户数据的紧耦合应用程序,缓存一致性未命中的作用更为显著。当我们考虑并行科学工作负载的性能时,我们将在附录 I 中详细分析它们的影响。

### 商业工作负载

在本节中,我们将研究一个4处理器共享内存多处理器在运行在线事务处理工作负载时的内存系统行为。我们所研究的研究是在1998年使用一台4处理器Alpha系统进行的,但它仍然是对这种工作负载的多处理器性能最全面和深刻的研究。我们将重点理解多处理器缓存活动,特别是L3中的行为,因为这里的大部分流量与一致性相关。

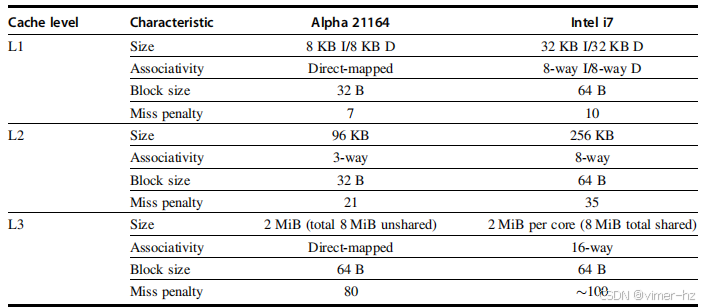

图5.9 本研究中使用的Alpha 21164和Intel i7的缓存层次结构特征。尽管i7的缓存大小更大且关联度更高,但未命中惩罚也更高,因此两者的行为可能仅略有不同。这两个系统在从私有缓存进行的数据传输时都有较高的惩罚(125个周期或更多)。一个关键的区别是,i7的L3缓存是共享的,而Alpha服务器则有四个独立的、不共享的缓存。

结果是在AlphaServer 4100上收集的,或者使用基于AlphaServer 4100模型的可配置模拟器进行收集。AlphaServer 4100中的每个处理器都是Alpha 21164,每个时钟周期能够发出多达四条指令,运行频率为300 MHz。尽管该系统中Alpha处理器的时钟频率明显低于2017年设计的系统中的处理器,但系统的基本结构,包括四发射处理器和三级缓存层次结构,与多核Intel i7及其他处理器非常相似,如图5.9所示。我们不关注性能细节,而是考虑模拟L3行为的数据,该数据涉及每个处理器的L3缓存大小从2到8 MiB不等。

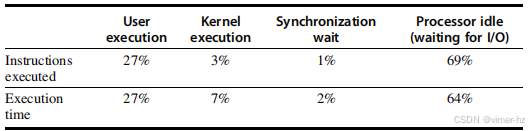

虽然原始研究考虑了三种不同的工作负载,但我们将重点关注以TPC-B为模型的在线事务处理(OLTP)工作负载(其内存行为类似于其较新的对应物TPC-C,如第一章所述),并使用Oracle 7.3.2作为底层数据库。该工作负载由一组生成请求的客户端进程和一组处理这些请求的服务器组成。服务器进程消耗了85%的用户时间,其余时间分配给客户端。尽管I/O延迟通过精心调整和足够的请求来隐藏,以保持处理器忙碌,但服务器进程通常在约25,000条指令后会因I/O而阻塞。总体而言,71%的执行时间是在用户模式下,18%在操作系统中,11%处于空闲状态,主要是等待I/O。

在所研究的商业应用中,OLTP应用对内存系统的压力最大,即使在评估更大L3缓存时也显示出显著的挑战。例如,在AlphaServer上,处理器大约有90%的周期处于停滞状态,内存访问占据了几乎一半的停滞时间,而L2未命中则占据了25%的停滞时间。

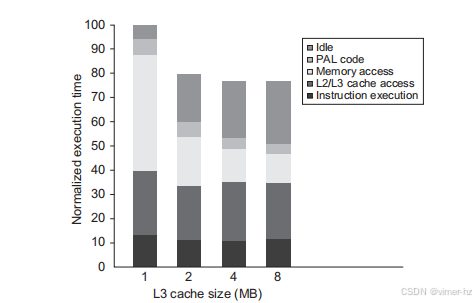

我们首先研究L3缓存大小变化的影响。在这些研究中,L3缓存的大小从每个处理器1 MiB变化到8 MiB;在每个处理器2 MiB时,L3的总大小与Intel i7 6700相等。然而,在i7的情况下,缓存是共享的,这带来了一些优缺点。共享的8 MiB缓存不太可能超过总大小为16 MiB的独立L3缓存。图5.10显示了使用二路组相联缓存增加缓存大小的影响,这减少了大量的冲突未命中。随着L3缓存的增大,执行时间得以改善,这是由于L3未命中的减少。令人惊讶的是,几乎所有的增益都是在从1 MiB增长到2 MiB(或四个处理器的总缓存从4 MiB增长到8 MiB)时实现的。尽管2 MiB和4 MiB缓存的未命中仍然导致显著的性能损失,但此后几乎没有额外的增益。问题是,为什么会这样?

图5.10 随着L3缓存大小从1 MiB增加到8 MiB(设置为二路组相联)的OLTP工作负载相对性能。随着缓存大小的增加,空闲时间也在增长,从而减少了一些性能提升。这种增长发生是因为内存系统的停滞减少,导致需要更多的服务器进程来覆盖I/O延迟。可以调整工作负载以提高计算/通信的平衡,从而控制空闲时间。PAL代码是一组在特权模式下执行的专用操作系统级指令序列;一个例子是TLB未命中处理程序。

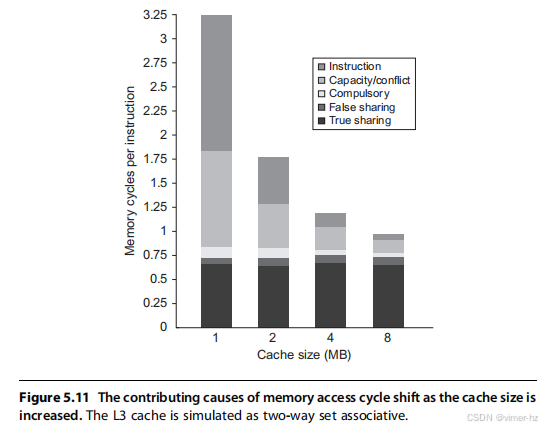

为了更好地理解这个问题的答案,我们需要确定哪些因素影响L3未命中率,以及当L3缓存增大时这些因素如何变化。图5.11显示了这些数据,展示了来自五个来源的每条指令贡献的内存访问周期数。1 MiB L3缓存的两个最大内存访问周期来源是指令未命中和容量/冲突未命中。随着L3缓存的增大,这两个来源缩小为次要贡献者。不幸的是,强制未命中、虚假共享和真实共享未命中不会受到更大L3缓存的影响。因此,在4和8 MiB时,真实共享未命中占据了未命中的主要比例;真实共享未命中的变化缺乏导致在将L3缓存大小增加到超过2 MiB时整体未命中率的减少有限。

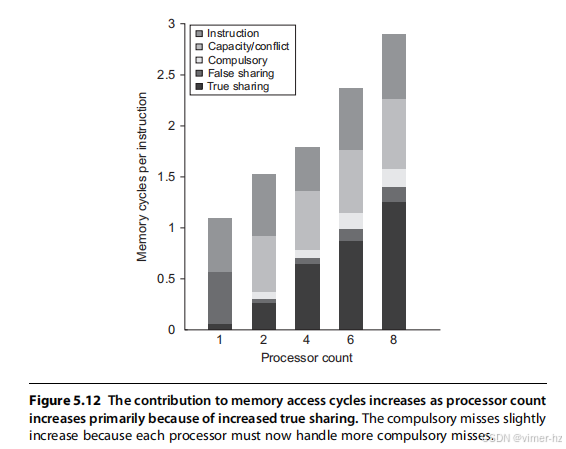

增加缓存大小消除了大部分单处理器未命中,同时对多处理器未命中影响不大。增加处理器数量如何影响不同类型的未命中呢?图5.12显示了这些数据,假设基准配置为2 MiB的二路组相联L3缓存(每个处理器的有效缓存大小与i7相同,但关联度较低)。正如我们所预期的,真实共享未命中率的增加并没有通过单处理器未命中的减少来进行补偿,导致每条指令的内存访问周期整体增加。

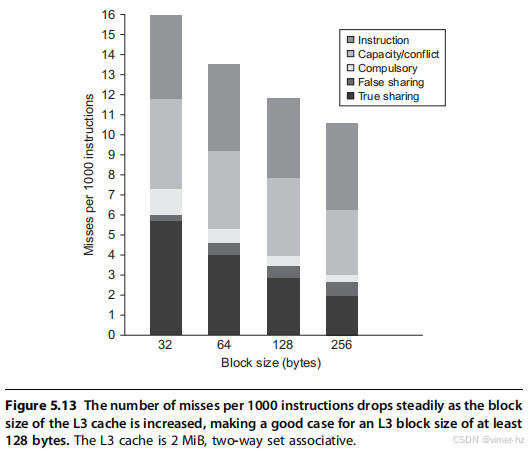

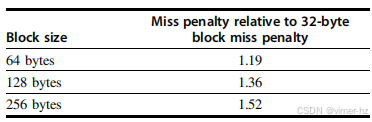

我们最后探讨的问题是,增加块大小是否对这个工作负载有帮助——这应该会降低指令未命中率和冷未命中率,并在一定范围内减少容量/冲突未命中率,可能还会降低真实共享未命中率。图5.13显示了随着块大小从32字节增加到256字节,每1000条指令的未命中次数。

增加块大小从32字节到256字节影响了四个未命中率组成部分:

- 真实共享未命中率减少了超过2倍,表明真实共享模式中存在一定的局部性。

- 强制未命中率显著下降,这符合我们的预期。

- 冲突/容量未命中率略有下降(与块大小增加8倍相比,仅减少1.26倍),表明在L3缓存大于2 MiB的单处理器未命中中,空间局部性并不高。

- 尽管绝对数值较小,虚假共享未命中率几乎翻倍。

指令未命中率没有显著变化令人惊讶。如果存在一个仅用于指令的缓存并表现出这种行为,我们可以得出结论,空间局部性非常差。在混合的L2和L3缓存情况下,指令-数据冲突等其他因素也可能导致更大块大小的高指令缓存未命中率。其他研究已记录了大型数据库和OLTP工作负载中指令流的低空间局部性,这些工作负载具有大量短基本块和专用代码序列。基于这些数据,使得更大块大小的L3性能与32字节块大小的L3相当的未命中惩罚,可以表示为32字节块大小惩罚的乘数。

随着现代DDR SDRAM使块访问变得快速,这些数字是可以实现的,特别是在64字节(i7块大小)和128字节块大小下。当然,我们还必须考虑增加内存流量带来的影响,以及可能与其他核心争用内存的情况。后者的影响可能很容易抵消通过提升单个处理器性能所获得的收益。

### 多道程序设计和操作系统工作负载

我们的下一个研究是一个多道程序工作负载,包含用户活动和操作系统活动。使用的工作负载是两个独立的安德鲁基准测试的编译阶段,该基准测试模拟软件开发环境。编译阶段由在八个处理器上执行的UNIX“make”命令的并行版本组成。该工作负载在八个处理器上运行5.24秒,创建了203个进程,并在三个不同的文件系统上执行了787个磁盘请求。工作负载使用128 MiB的内存,并且没有发生页面调度活动。

该工作负载有三个明显的阶段:编译基准,这涉及大量计算活动;将目标文件安装到库中;以及删除目标文件。最后一个阶段完全被I/O占主导地位,只有两个进程处于活跃状态(每个运行一个)。在中间阶段,I/O也发挥了主要作用,而处理器大部分时间处于空闲状态。总体工作负载比OLTP工作负载更具系统和I/O密集性。

对于工作负载的测量,我们假设以下内存和I/O系统:

- **一级指令缓存**——32 KB,双路组相联,块大小64字节,命中时间1个时钟周期。

- **一级数据缓存**——32 KB,双路组相联,块大小32字节,命中时间1个时钟周期。我们关注的是一级数据缓存的行为,与专注于L3缓存的OLTP研究形成对比。

- **二级缓存**——1 MiB统一,双路组相联,块大小128字节,命中时间10个时钟周期。

- **主内存**——单一内存在总线上,访问时间为100个时钟周期。

- **磁盘系统**——固定访问延迟为3毫秒(低于正常水平以减少空闲时间)。

图5.14 显示了多道程序并行“make”工作负载中执行时间的分布。高比例的空闲时间是由于当只有八个处理器中的一个处于活动状态时,磁盘延迟造成的。这些数据以及后续对该工作负载的测量是通过SimOS系统收集的(Rosenblum等,1995年)。实际的运行和数据收集由斯坦福大学的M. Rosenblum、S. Herrod和E. Bugnion完成。

图5.14展示了使用刚刚列出的参数时,八个处理器的执行时间分解。执行时间被分为四个组件:

1. 空闲——在内核模式空闲循环中的执行

2. 用户——在用户代码中的执行

3. 同步——执行或等待同步变量

4. 内核——在操作系统中执行的,既不是空闲也不是在同步访问中的部分

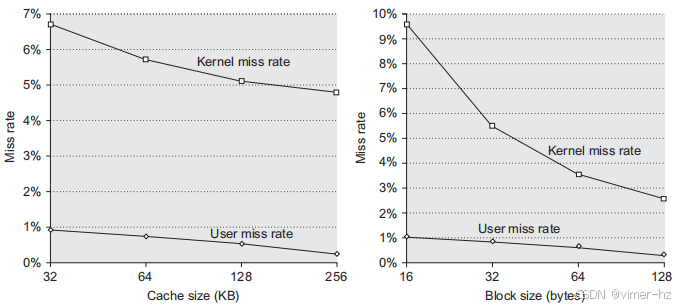

该多道程序工作负载在指令缓存性能上存在显著损失,至少对于操作系统而言。对于64字节块大小的双向组相联缓存,操作系统中的指令缓存缺失率从32 KB缓存的1.7%下降到256 KB缓存的0.2%。在各种缓存大小下,用户级指令缓存缺失率大约是操作系统缺失率的六分之一。这部分解释了尽管用户代码执行的指令数量是内核的九倍,但这些指令的执行时间仅约为内核执行的较少指令所需时间的四倍。

### 多道程序和操作系统工作负载的性能

在本节中,我们将分析多道程序工作负载在缓存大小和块大小变化时的缓存性能。由于内核和用户进程之间行为的差异,我们将这两部分分开讨论。但请记住,用户进程执行的指令数量超过八倍,因此总体缺失率主要由用户代码中的缺失率决定,而如我们所见,用户缺失率通常是内核缺失率的五分之一。

尽管用户代码执行更多的指令,但操作系统的行为可能会导致比用户进程更多的缓存缺失,这主要有两个原因,除了更大的代码大小和局部性缺失外。首先,内核在将所有页面分配给用户之前会先初始化它们,这显著增加了内核缺失率的强制组件。其次,内核实际上共享数据,因此具有不容忽视的一致性缺失率。相比之下,用户进程只有在被调度到不同处理器时才会导致一致性缺失,而这一缺失率的成分相对较小。这是多道程序工作负载与OLTP工作负载之间的一个主要区别。

图5.15显示了内核和用户组件在数据缺失率与数据缓存大小和块大小之间的关系。增加数据缓存大小对用户缺失率的影响大于对内核缺失率的影响。增加块大小对两者的缺失率都有积极的影响,因为较大比例的缺失来自强制性和容量缺失,而这两者都可以通过增大块大小来改善。由于一致性缺失相对较少,增加块大小的负面影响也较小。为了理解内核和用户进程的行为差异,我们可以观察内核缺失的表现。

图5.15 用户和内核组件的数据缺失率在L1数据缓存大小增加(左侧)与L1数据缓存块大小增加(右侧)时表现出不同的行为。当将L1数据缓存从32 KB增加到256 KB(使用32字节块)时,用户缺失率的下降幅度明显大于内核缺失率的下降幅度:用户级缺失率几乎下降了3倍,而内核级缺失率仅下降了1.3倍。在最大缓存大小时,L1的大小接近现代多核处理器中L2的大小。因此,这些数据表明,在L2缓存中,内核缺失率仍然会显著。随着L1块大小的增加(保持L1缓存为32 KB),用户和内核组件的缺失率均稳步下降。与增加缓存大小的影响相比,增加块大小对内核缺失率的改善更为显著(当块从16字节增加到128字节时,内核引用的缺失率下降接近4倍,而用户引用的缺失率下降不到3倍)。

图5.16显示了内核缺失率在缓存大小和块大小增加时的变化。缺失被分为三类:强制性缺失、一致性缺失(包括真实共享和虚假共享)以及容量/冲突缺失(其中包括操作系统与用户进程之间的干扰造成的缺失,以及多个用户进程之间的干扰)。图5.16确认,对于内核引用,增加缓存大小仅减少单处理器的容量/冲突缺失率。相比之下,增加块大小会减少强制性缺失率。随着块大小的增加,一致性缺失率没有大幅上升,这表明虚假共享效应可能并不显著,尽管这些缺失可能在一定程度上抵消了减少真实共享缺失带来的收益。

图5.16 当在八个处理器上运行多程序工作负载时,L1数据缓存大小从32 KB增加到256 KB时,内核数据缺失率的各个组成部分发生变化。强制缺失率组件保持不变,因为它不受缓存大小的影响。容量组件下降了超过2倍,而一致性组件几乎翻倍。一致性缺失的增加是因为随着缓存大小的增加,由无效化导致缺失的概率上升,因为由于容量原因被替换的条目更少。正如我们所预期的,L1数据缓存块大小的增加显著降低了内核引用中的强制缺失率。它对容量缺失率也产生了显著影响,使其在不同块大小范围内下降了2.4倍。增大的块大小对一致性流量有小幅减少,似乎在64字节时趋于稳定,且在使用128字节行时一致性缺失率没有变化。由于随着块大小的增加一致性缺失率没有显著下降,因此由一致性造成的缺失率比例从大约7%增长到大约15%。

如果我们查看每个数据引用所需的字节数,如图5.17所示,我们会发现内核的流量比率随着块大小的增加而增加。这种情况的原因很容易理解:当从16字节块切换到128字节块时,缺失率降低了约3.7倍,但每次缺失传输的字节数增加了8,因此总的缺失流量增加了略超过2倍。用户程序在块大小从16字节增加到128字节时也增加了超过2倍,但它起始时的水平要低得多。

对于多程序工作负载,操作系统对内存系统的需求要大得多。如果在工作负载中包含更多的操作系统或类似操作系统的活动,并且其行为与本工作负载的测量相似,那么构建一个足够强大的内存系统将变得非常困难。提升性能的一种可能途径是通过更好的编程环境或程序员的帮助,使操作系统更具缓存意识。例如,操作系统会重用来自不同系统调用的请求所占用的内存。尽管被重用的内存将被完全覆盖,但硬件由于未能识别这一点,会试图保持一致性,并假设某些缓存块的部分内容可能会被读取,即使实际上并不会。这种行为类似于在过程调用中重用栈位置。IBM Power 系列支持编译器在过程调用中指示这种行为,而最新的 AMD 处理器也有类似的支持。操作系统检测这种行为较为困难,可能需要程序员的协助,但潜在的收益可能更大。

操作系统和商业工作负载对多处理器内存系统提出了严峻的挑战,与我们在附录 I 中研究的科学应用不同,这些工作负载不太适合算法或编译器重构。随着核心数量的增加,预测此类应用程序的行为可能会变得更加困难。能够模拟数十到数百个核心的大型应用程序(包括操作系统)的仿真或模拟方法将对维持分析和定量设计方法至关重要。

5.4 Distributed Shared-Memory and Directory-Based Coherence

如我们在第5.2节中所见,监视协议在每次缓存未命中时都需要与所有缓存进行通信,包括对可能共享数据的写入。缺乏任何集中式数据结构来跟踪缓存状态既是基于监视方案的基本优势,因为这使其成本低廉,同时也是其在可扩展性方面的致命弱点。

例如,考虑一个由四个四核多核处理器组成的多处理器系统,这些处理器能够在4 GHz的时钟下每个时钟周期支持一个数据引用。从附录I的第I.5节中的数据来看,应用程序可能需要4到170 GiB/s的内存总线带宽。支持两个DDR4内存通道的i7的最大内存带宽为34 GiB/s。如果多个i7多核处理器共享同一内存系统,它们将很容易使其超负荷。在过去几年中,多核处理器的发展迫使所有设计者转向某种形式的分布式内存,以支持各个处理器的带宽需求。

我们可以通过分布内存来增加内存带宽和互连带宽,如第373页的图5.2所示;这立即将本地内存流量与远程内存流量分开,从而减少对内存系统和互连网络的带宽需求。除非我们消除一致性协议在每次缓存未命中时广播的需求,否则分布内存所带来的收益有限。

如我们之前提到的,监视协议的替代方案是目录协议。目录维护可能被缓存的每个块的状态。目录中的信息包括哪些缓存(或缓存集合)拥有该块的副本、该块是否为脏块等等。在具有共享最外层缓存(例如L3)的多核系统中,实现目录方案非常简单:只需为每个L3块保持一个与核心数量相等的位向量。该位向量指示哪些私有L2缓存可能拥有L3中的块副本,失效信息仅发送给这些缓存。如果L3是包含的,这对单个多核系统来说效果很好,而这种方案正是Intel i7所使用的。

在多核系统中使用单一目录的解决方案并不具备可扩展性,即使它避免了广播。目录必须是分布式的,但分布方式必须让一致性协议知道如何找到任何缓存的内存块的目录信息。显而易见的解决方案是将目录与内存一起分布,使得不同的一致性请求可以发送到不同的目录,就像不同的内存请求发送到不同的内存一样。如果信息保存在像L3这样的外部缓存中,并且是多银行的,则目录信息可以与不同的缓存银行一起分布,从而有效地增加带宽。

分布式目录保持了块的共享状态始终位于一个已知位置的特性。这个属性加上维护其他节点可能缓存该块的信息,使得一致性协议能够避免广播。图5.18展示了我们分布式内存多处理器的结构,目录被添加到每个节点。

图5.18 在每个节点添加了一个目录,以实现分布式内存多处理器中的缓存一致性。在这种情况下,节点被表示为单个多核芯片,相关内存的目录信息可以位于多核芯片内或外部。每个目录负责跟踪共享该节点内存地址的缓存。一致性机制将处理目录信息的维护以及多核节点内所需的任何一致性操作。

最简单的目录实现将目录中的条目与每个内存块关联。在这些实现中,信息量与内存块数量(每个块大小与L2或L3缓存块相同)与节点数量的乘积成正比,其中节点是单个多核处理器或小型处理器集合,这些处理器在内部实现一致性。对于少于几百个处理器的多处理器系统(每个处理器可能是多核),这种开销并不成问题,因为合理块大小下的目录开销是可以接受的。

对于更大的多处理器系统,我们需要方法来有效扩展目录结构,但只有超级计算机级别的系统需要担心这一点。

### 基于目录的缓存一致性协议:基础

与监听协议一样,目录协议必须实施两个主要操作:处理读取未命中和处理对共享、干净缓存块的写入(处理对当前共享块的写未命中是这两者的简单组合)。为了实现这些操作,目录必须跟踪每个缓存块的状态。在一个简单的协议中,这些状态可以是:

- **共享**——一个或多个节点缓存了该块,内存中的值是最新的(在所有缓存中也是如此)。

- **未缓存**——没有节点有该缓存块的副本。

- **修改**——恰好有一个节点有该缓存块的副本,并且已经写入该块,因此内存中的副本已过期。这个处理器被称为该块的所有者。

除了跟踪每个潜在共享内存块的状态外,我们还需要跟踪哪些节点有该块的副本,因为在写入时需要使这些副本失效。最简单的方法是为每个内存块保留一个位向量。当该块被共享时,位向量的每一位表示相应的处理器芯片(通常是多核)是否有该块的副本。当该块处于独占状态时,我们也可以利用位向量来跟踪该块的所有者。出于效率考虑,我们还在各个缓存中跟踪每个缓存块的状态。

每个缓存的状态机的状态和转换与我们在监听缓存中使用的相同,尽管转换时的操作略有不同。使无效和定位数据项的独占副本的过程不同,因为它们都涉及请求节点与目录之间以及目录与一个或多个远程节点之间的通信。在监听协议中,这两个步骤通过广播给所有节点的方式结合在一起。

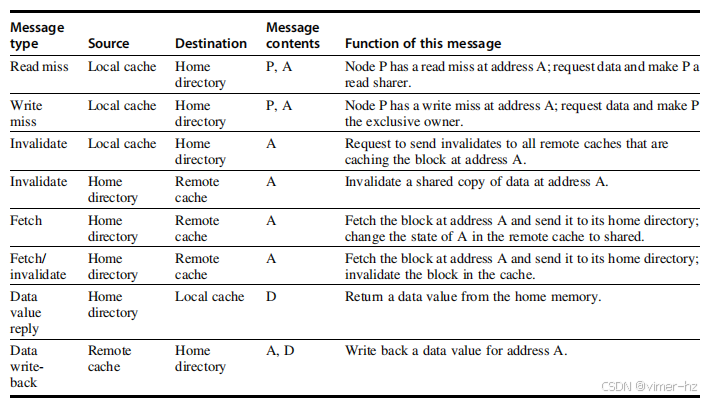

在查看协议状态图之前,审视一系列可能在处理未命中和保持一致性时在处理器和目录之间发送的消息类型是有用的。图5.19展示了节点之间发送的消息类型。**本地节点**是请求发起的节点。**主节点**是存储内存位置和地址的目录条目的节点。物理地址空间是静态分布的,因此包含给定物理地址的内存和目录的节点是已知的。例如,高位可能提供节点编号,而低位提供该节点内存中的偏移量。本地节点也可能是主节点。当主节点是本地节点时,必须访问目录,因为副本可能存在于第三个节点,即远程节点。

图5.19 节点之间为维护一致性而发送的可能消息,包括源节点和目标节点、内容(其中 P5 为请求节点编号,A5 为请求地址,D5 为数据内容)以及消息的功能。前三条消息是本地节点向主节点发送的请求。第四到第六条消息是当主节点需要数据以满足读取或写入未命中请求时,发送给远程节点的消息。数据值回复用于将值从主节点发送回请求节点。数据值回写发生有两个原因:一是当缓存中的块被替换并且必须写回到其主存时,二是作为对来自主节点的获取或获取/失效消息的回复。每当块变为共享时写回数据值简化了协议中的状态数量,因为任何脏块必须是独占的,而任何共享块总是可以在主存中找到。

远程节点是指拥有缓存块副本的节点,无论是独占(在这种情况下,它是唯一的副本)还是共享。远程节点可以与本地节点或主节点相同。在这种情况下,基本协议不变,但处理器之间的消息可能会被处理器内部的消息所替代。

在本节中,我们假设一种简单的内存一致性模型。为了最小化消息类型和协议复杂性,我们假设消息将按照发送顺序接收和处理。这个假设在实际中可能并不成立,可能导致额外的复杂性,其中一些问题将在5.6节讨论内存一致性模型时得到解决。在本节中,我们使用这个假设来确保节点发送的失效消息在新消息传输之前得到响应,这与我们在实现监听协议时的假设一致。与监听案例一样,我们省略了一些实施一致性协议所需的细节。特别是,写操作的序列化以及确认写操作的失效已经完成并不像基于广播的监听机制那样简单。相反,需要对写未命中和失效请求进行明确的确认。我们将在附录I中更详细地讨论这些问题。

### 目录协议示例

在基于目录的协议中,缓存块的基本状态与监听协议中的状态完全相同,目录中的状态也类似于我们之前展示的。因此,我们可以首先从简单的状态图开始,显示单个缓存块的状态转换,然后检查与内存中每个块对应的目录项的状态图。与监听案例一样,这些状态转换图并不代表一致性协议的所有细节;然而,实际控制器高度依赖于多处理器的多个细节(消息传递特性、缓冲结构等)。在本节中,我们呈现基本的协议状态图。实现这些状态转换图所涉及的棘手问题将在附录I中讨论。

图5.20展示了单个缓存对协议操作的响应。我们使用与上一节相同的符号,来自节点外部的请求用灰色表示,操作用粗体字表示。单个缓存的状态转换是由读取未命中、写入未命中、失效和数据获取请求引起的;图5.20显示了这些操作。单个缓存还会生成发送到主目录的读取未命中、写入未命中和失效消息。读取和写入未命中需要数据值的回复,这些事件在改变状态之前会等待回复。知道失效何时完成是一个独立的问题,并将单独处理。

图5.20 显示了基于目录的系统中单个缓存块的状态转移图。来自本地处理器的请求用黑色表示,而来自主目录的请求用灰色表示。状态与监听案例中的状态相同,事务也非常相似,显式的失效和写回请求取代了之前在总线上广播的写未命中请求。与监听控制器相同,我们假设对共享缓存块的写入尝试被视为未命中;实际上,这种事务可以被视为所有权请求或升级请求,并且可以在不需要获取缓存块的情况下交付所有权。

图5.20中缓存块的状态转换图的操作本质上与监听案例相同:状态是相同的,刺激几乎也是相同的。在监听方案中,通过总线(或其他网络)广播的写入未命中操作被目录控制器选择性发送的数据获取和失效操作所替代。与监听协议一样,任何缓存块在被写入时必须处于独占状态,任何共享块在内存中必须是最新的。在许多多核处理器中,处理器缓存的最外层在各核心之间是共享的(如Intel i7、AMD Opteron和IBM Power7中的L3),而该级别的硬件维护着同一芯片上各核心私有缓存之间的一致性,使用内部目录或监听机制。因此,片上多核一致性机制可以通过接口连接到最外层共享缓存,将一致性扩展到更大集的处理器。由于此接口位于L3,因此处理器与一致性请求之间的争用问题较小,从而可以避免复制标签。

在基于目录的协议中,目录实现了一致性协议的另一半。发送到目录的消息会引发两种不同类型的操作:更新目录状态和发送额外消息以满足请求。目录中的状态表示缓存块的三种标准状态;然而,与监听方案不同,目录状态指示的是所有缓存副本的内存块状态,而不仅仅是单个缓存块。

内存块可能在任何节点上未缓存,也可能在多个节点上缓存且可读(共享),或者在一个节点上独占缓存且可写。除了每个块的状态外,目录还必须跟踪拥有该块副本的节点集合;我们使用一个称为“共享者”(Sharers)的集合来执行此功能。在节点少于64个的多处理器系统中(每个节点可能代表四到八个处理器),该集合通常以位向量的形式存储。目录请求需要更新共享者集合,并且还需读取该集合以执行失效操作。

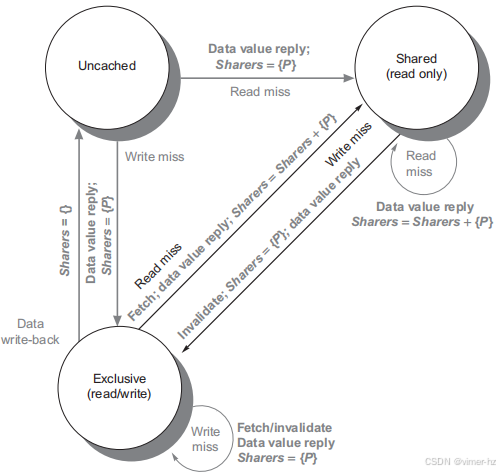

图5.21 目录的状态转换图与单个缓存的转换图具有相同的状态和结构。所有操作均以灰色显示,因为它们都是由外部引起的。粗体表示目录对请求所采取的行动。

图5.21 显示了目录在收到消息后的操作。目录接收到三种不同的请求:读未命中、写未命中和数据写回。目录响应发送的消息以粗体显示,更新共享者集合的操作以粗斜体显示。由于所有刺激消息都是外部的,因此所有操作都用灰色表示。我们简化的协议假设某些操作是原子的,例如请求一个值并将其发送到另一个节点;而现实中的实现无法使用这一假设。

为了理解这些目录操作,我们逐状态检查所收到的请求和采取的行动。当一个块处于未缓存状态时,内存中的副本就是当前值,因此该块唯一可能的请求为:

- **读未命中**——请求节点从内存中获取请求的数据,并且请求者成为唯一的共享节点。该块的状态变为共享。

- **写未命中**——请求节点获得该值并成为共享节点。该块状态变为独占,以表明唯一有效副本已被缓存。共享者指示所有者的身份。

当块处于共享状态时,内存值是最新的,因此可以发生相同的两种请求:

- **读未命中**——请求节点从内存中获取请求的数据,并且请求节点被添加到共享集合中。

- **写未命中**——请求节点获取该值。所有在共享者集合中的节点都会收到失效消息,并且共享者集合将包含请求节点的身份。该块的状态变为独占。

当块处于独占状态时,块的当前值保存在由共享者集合(所有者)标识的节点的缓存中,因此有三种可能的目录请求:

- **读未命中**——向所有者发送数据获取消息,这会导致所有者缓存中的块状态转换为共享,并使所有者将数据发送到目录,在那里写入内存并返回给请求的处理器。请求节点的身份被添加到共享者集合中,该集合仍包含原所有者的身份(因为它仍然有一个可读副本)。

- **数据写回**——所有者正在替换该块,因此必须将其写回。这次写回使内存副本保持最新(主目录本质上成为所有者),该块现在变为未缓存状态,且共享者集合为空。

- **写未命中**——块有了新的所有者。向旧所有者发送消息,导致缓存失效该块并将值发送到目录,然后再发送到请求节点,该节点成为新所有者。共享者集合被设置为新所有者的身份,块的状态保持为独占。

图5.21中的状态转换图是一种简化,就像在监听缓存情况下那样。在目录和使用非总线网络实现的监听方案的情况下,我们的协议需要处理非原子内存事务。附录I深入探讨了这些问题。

在实际多处理器中使用的目录协议包含额外的优化。特别是在此协议中,当独占块发生读或写未命中时,块首先被发送到主节点的目录。从那里,它被存储到主内存并发送到最初请求的节点。

许多在商业多处理器中使用的协议直接将数据从所有者节点转发到请求节点(同时执行写回到主内存)。这样的优化通常通过增加死锁的可能性和需要处理的消息类型来增加复杂性。

实现目录方案需要解决与我们讨论的监听协议大部分相同的挑战。然而,还有一些新的附加问题,我们在附录I中进行了描述。在第5.8节中,我们简要介绍了现代多核如何将一致性扩展到单个芯片之外。多芯片一致性和多核一致性的组合包括所有四种可能性:监听/监听(AMD Opteron)、监听/目录、目录/监听以及目录/目录!许多多处理器选择在单个芯片内采用某种形式的监听,这在外层缓存共享且包含时特别有吸引力,而跨多个芯片则使用目录。这种方法简化了实现,因为只需跟踪处理器芯片,而不是单个核心。

5.5 Synchronization: The Basics

同步机制通常是通过依赖于硬件提供的同步指令的用户级软件例程构建的。对于较小的多处理器或低争用情况,关键的硬件能力是不可中断的指令或指令序列,能够原子性地检索和修改一个值。然后,软件同步机制基于这一能力构建。在本节中,我们重点讨论锁定和解锁同步操作的实现。锁定和解锁可以直接用于创建互斥,以及实现更复杂的同步机制。

在高争用情况下,同步可能成为性能瓶颈,因为争用会引入额外的延迟,并且在这样的多处理器中,延迟可能更大。我们在附录I中讨论了如何将本节的基本同步机制扩展到大处理器数量的情况。

### 基本硬件原语

我们在多处理器中实现同步所需的关键能力是一组硬件原语,能够原子性地读取和修改内存位置。如果没有这样的能力,构建基本同步原语的成本将过高,并且随着处理器数量的增加而增加。有多种基本硬件原语的替代形式,它们都提供原子性读取和修改位置的能力,并且有某种方法来判断读取和写入是否是原子执行的。这些硬件原语是构建各种用户级同步操作的基本构件,包括锁和屏障等内容。一般来说,架构师并不期望用户直接使用基本硬件原语,而是希望系统程序员利用这些原语构建同步库,这个过程往往复杂且棘手。

让我们从一种这样的硬件原语开始,展示它如何用于构建一些基本的同步操作。

一种构建同步操作的典型操作是原子交换,它将寄存器中的值与内存中的值互换。为了说明如何使用这一方法构建基本的同步操作,假设我们想构建一个简单的锁,其中值0表示锁是空闲的,而值1表示锁不可用。处理器通过将寄存器中的值1与对应于锁的内存地址进行交换来尝试设置锁。从交换指令返回的值是1(如果其他处理器已经声称访问权限)或0。在后者的情况下,值也会被改为1,从而防止任何竞争的交换再次获取到0。例如,考虑两个处理器同时尝试进行交换:这个竞争会被打破,因为恰好有一个处理器会先执行交换,返回0,而第二个处理器在执行交换时将返回1。使用交换(或置换)原语实现同步的关键在于操作是原子的:交换是不可分割的,并且两个同时进行的交换会被写入序列化机制所排序。因此,两个处理器不能同时确认它们已设置同步变量。

还有其他一些原子原语可以用于实现同步。它们都有一个关键特性,即以某种方式读取和更新内存值,使我们能够判断这两个操作是否以原子方式执行。一种在许多旧多处理器中存在的操作是测试并设置,它先测试一个值,如果值通过测试,则设置该值。例如,我们可以定义一个操作,测试值是否为0并将其设置为1,这可以像使用原子交换一样使用。另一个原子同步原语是取出并递增:它返回一个内存位置的值并原子性地递增该值。通过使用值0来表示同步变量未被占用,我们可以像使用交换一样使用取出并递增。还有其他使用取出并递增等操作的方法,我们将很快看到。

实现单个原子内存操作会带来一些挑战,因为这要求在一个不可中断的指令中同时进行内存读取和写入。这一要求使得一致性实现变得复杂,因为硬件不能在读取和写入之间允许任何其他操作,同时又必须避免死锁。

另一种选择是使用一对指令,其中第二条指令返回一个值,通过该值可以推断出这一对指令是否以原子方式执行。如果看起来所有其他由任何处理器执行的操作都发生在这一对指令之前或之后,那么这一对指令就是有效原子的。因此,当一对指令有效原子时,没有其他处理器可以在这一对指令之间更改值。这正是MIPS处理器和RISC-V采用的方法。

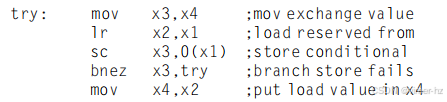

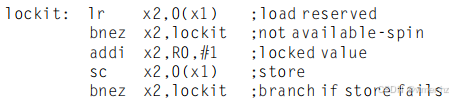

在 RISC-V 中,这对指令包括一个特殊的加载指令,称为保留加载(也称为链接加载或锁定加载),以及一个特殊的存储指令,称为条件存储。保留加载将由 rs1 指定的内存内容加载到 rd 中,并在该内存地址上创建一个保留。条件存储将 rs2 中的值存储到由 rs1 指定的内存地址。如果加载的保留因对同一内存位置的写入而被打破,则条件存储失败,并将非零值写入 rd;如果成功,则条件存储写入 0。如果处理器在这两条指令之间进行上下文切换,则条件存储总是失败。这些指令是按顺序使用的,因为保留加载返回初始值,而条件存储只有在成功时才返回 0,因此以下序列在由 x1 的内容指定的内存位置与 x4 中的值之间实现了原子交换:

在这个序列结束时,x4 的内容与由 x1 指定的内存位置已经被原子性地交换。每当处理器介入并在 lr 和 sc 指令之间修改内存中的值时,sc 会在 x3 中返回 0,从而导致代码序列重试。

保留加载/条件存储机制的一个优点是它可以用来构建其他同步原语。例如,下面是一个原子取出并递增的操作:

这些指令通常通过在一个寄存器中跟踪 lr 指令指定的地址来实现,这个寄存器通常称为保留寄存器。如果发生中断,或者链接寄存器中匹配地址的缓存块被失效(例如,由另一个 sc 指令),则链接寄存器会被清除。sc 指令简单地检查其地址是否与保留寄存器中的地址匹配。如果匹配,sc 就成功;否则,就失败。由于条件存储在对加载保留地址的另一次尝试存储或任何异常后都会失败,因此在选择插入这两条指令之间的指令时必须小心。特别是,只有寄存器到寄存器的指令可以安全地被允许;否则,可能会导致死锁情况,使处理器无法完成 sc。此外,在保留加载和条件存储之间的指令数量应尽量减少,以降低无关事件或竞争处理器频繁导致条件存储失败的概率。

### 使用一致性实现锁

一旦我们有了原子操作,就可以利用多处理器的缓存一致性机制来实现自旋锁——一种处理器持续尝试获取的锁,直到成功为止。自旋锁在程序员预期锁会被持有很短时间,并希望在锁可用时获取锁的延迟尽可能低的情况下使用。由于自旋锁会占用处理器在循环中等待锁释放,因此在某些情况下它们是不合适的。

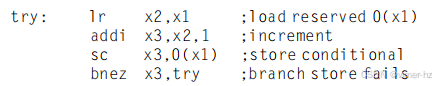

最简单的实现(如果没有缓存一致性)是将锁变量保存在内存中。处理器可以不断尝试使用原子操作(例如,原子交换)来获取锁,并测试交换是否返回锁为空。要释放锁,处理器只需将值 0 存储到锁中。下面是锁定自旋锁的代码序列,其地址在 x1 中。它使用 EXCH 作为第 414 页的原子交换序列的宏:

如果我们的多处理器支持缓存一致性机制,我们可以利用这一机制对锁进行缓存,以保持锁值的一致性。缓存锁有两个优点。首先,它允许在“自旋”过程(尝试在紧密循环中测试并获取锁)中使用本地缓存副本,而不是在每次尝试获取锁时都进行全局内存访问。第二个优点源于对锁访问的局部性观察;也就是说,最后使用锁的处理器在不久的将来会再次使用它。在这种情况下,锁值可能存储在该处理器的缓存中,从而大大减少获取锁的时间。

获得第一个优点——能够在本地缓存副本上自旋,而不是在每次尝试获取锁时生成内存请求——需要对我们简单的自旋过程进行更改。在前面的循环中,每次尝试交换都需要写操作。如果多个处理器尝试获取锁,每个处理器都会生成写操作。其中大多数写操作将导致写失效,因为每个处理器都在尝试以独占状态获取锁变量。因此,我们应该修改自旋锁程序,使其通过在本地复制的锁上进行读取自旋,直到成功看到锁可用为止。然后,它尝试通过执行交换操作来获取锁。

处理器首先读取锁变量以测试其状态。处理器会持续读取和测试,直到读取值表明锁是解锁的。然后,处理器与所有其他同样在“自旋等待”的进程竞争,看看哪个能首先锁定变量。所有进程都使用一个交换指令,该指令读取旧值并将 1 存储到锁变量中。唯一的赢家会看到 0,而失败者看到的是赢家放置的 1。(失败者将继续将变量设置为锁定值,但这并不重要。)获胜的处理器在锁后执行代码,完成后将 0 存储到锁变量中以释放锁,从而重新开始竞争。以下是执行此自旋锁的代码(请记住,0 表示解锁,1 表示锁定):

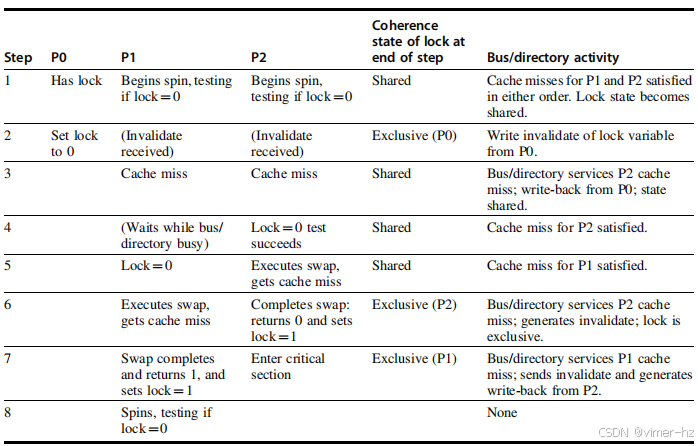

让我们来看看这个“自旋锁”方案是如何利用缓存一致性机制的。图5.22展示了多个进程使用原子交换尝试锁定变量时的处理器和总线或目录操作。一旦持有锁的处理器将0存入锁中,所有其他缓存都会被失效,必须获取新值以更新它们的锁副本。其中一个缓存首先获取到解锁值(0)的副本并执行交换。当其他处理器的缓存未命中被满足时,它们发现变量已经被锁定,因此必须返回继续测试和自旋。

图5.22 展示了三个处理器 P0、P1 和 P2 的缓存一致性步骤和总线流量。该图假设采用写失效一致性。P0 在步骤 1 开始时持有锁,锁的值为 1(即,锁定状态);在步骤 1 开始之前,它最初是独占的,并由 P0 拥有。P0 退出并解锁(步骤 2)。P1 和 P2 竞争,看看哪个能在交换过程中读取到解锁值(步骤 3-5)。P2 胜出并进入临界区(步骤 6 和 7),而 P1 的尝试失败,因此它开始自旋等待(步骤 7 和 8)。在实际系统中,这些事件将花费远超过 8 个时钟周期,因为获取总线和响应未命中的时间要长得多。一旦达到步骤 8,过程可以与 P2 重复,最终获得独占访问权并将锁设置为 0。

这个例子展示了加载保留/条件存储原语的另一个优点:读写操作被明确分开。加载保留操作不需要引起任何总线流量。这一事实允许如下简单的代码序列,它具有与使用交换的优化版本相同的特征(x1是锁的地址,lr替代了LD,sc替代了EXCH):

第一个分支形成自旋循环;第二个分支在两个处理器同时看到锁可用时解决竞争条件。

5.6 Models of Memory Consistency: An Introduction

缓存一致性确保多个处理器看到内存的一致视图。它并没有回答内存视图必须有多一致的问题。我们所说的“多一致”实际上是在询问,一个处理器何时必须看到另一个处理器更新的值。由于处理器通过共享变量进行通信(这些变量既用于数据值也用于同步),问题归结为:处理器必须以什么顺序观察另一个处理器的数据写入?由于“观察另一个处理器的写入”的唯一方式是通过读取,因此问题变成了不同处理器在对不同位置进行读写时,必须强制执行哪些属性?

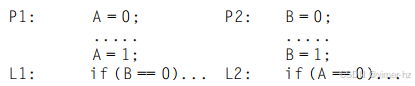

尽管内存必须保持多一致的问题看似简单,但实际上非常复杂,这一点可以通过一个简单的例子来说明。以下是来自 P1 和 P2 进程的两个代码段,呈并排显示:

假设这些进程在不同的处理器上运行,并且位置 A 和 B 最初都被两个处理器缓存,初始值为 0。如果写入操作总是立即生效并被其他处理器看到,那么两个 IF 语句(标记为 L1 和 L2)都无法同时评估为真,因为达到 IF 语句意味着 A 或 B 必须被赋值为 1。但假设写入失效被延迟,并且处理器在此延迟期间被允许继续执行。那么 P1 和 P2 可能在尝试读取值之前,都没有看到对 B 和 A 的失效。现在的问题是,这种行为是否应该被允许,如果允许,应该在什么条件下?

内存一致性的最简单模型称为顺序一致性。顺序一致性要求任何执行的结果都与每个处理器的内存访问按顺序执行,并且不同处理器之间的访问可以任意交错的情况相同。顺序一致性消除了在前一个示例中某些不明显执行的可能性,因为赋值必须在启动 IF 语句之前完成。

实现顺序一致性的最简单方法是要求处理器在完成所有因该内存访问而导致的失效之前,延迟任何内存访问的完成。当然,延迟下一个内存访问直到上一个访问完成也是同样有效的。记住,内存一致性涉及不同变量之间的操作:必须排序的两个访问实际上是指向不同的内存位置。在我们的例子中,我们必须延迟对 A 或 B 的读取(A == 0 或 B == 0),直到之前的写入完成(B=1 或 A=1)。在顺序一致性下,我们不能仅仅将写入放入写缓冲区然后继续读取。

尽管顺序一致性提供了一个简单的编程范式,但它降低了潜在的性能,特别是在具有大量处理器或长互连延迟的多处理器系统中,如以下示例所示。

**示例** 假设我们有一个处理器,其中写入失效需要 50 个周期来建立所有权,在所有权建立后,每个失效发出需要 10 个周期,并且一旦发出,失效完成并被确认需要 80 个周期。假设还有四个其他处理器共享一个缓存块,如果处理器是顺序一致的,写入失效会让写入处理器停滞多长时间?假设在获得写入失效的所有权后,我们可以继续执行而不必等待失效;那么写入将花费多长时间?

**回答** 当我们等待失效时,每次写入的总时间是所有权时间加上完成失效的时间。由于失效可以重叠,我们只需关注最后一个失效,它在所有权建立后 10 + 10 + 10 + 10 = 40 周期开始。因此,写入的总时间为 50 + 40 + 80 = 170 周期。相比之下,所有权时间仅为 50 个周期。通过适当的写缓冲区实现,甚至可以在所有权建立之前继续执行。

为了提供更好的性能,研究人员和架构师探索了两条不同的路线。首先,他们开发了雄心勃勃的实现,这些实现保持了顺序一致性,但使用延迟隐藏技术来减少惩罚;我们将在第 5.7 节讨论这些技术。其次,他们开发了不太严格的内存一致性模型,以允许更快的硬件。这些模型可能会影响程序员对多处理器的看法,因此在讨论这些不太严格的模型之前,让我们看看程序员的期望是什么。

### 程序员的视角

尽管顺序一致性模型在性能上存在劣势,但从程序员的角度来看,它具有简单性的优势。挑战在于开发一种简单易懂的编程模型,同时又能实现高性能的实现。

一种允许我们实现更高效实现的编程模型是假设程序是同步的。如果所有对共享数据的访问都通过同步操作进行排序,则该程序被认为是同步的。当一个处理器对变量进行写入,另一个处理器对该变量进行访问(无论是读取还是写入)时,如果在每种可能的执行中,这两个操作之间由一对同步操作分隔,则称该数据引用是有序的。这对同步操作包括一个在写入之后由写入处理器执行的操作,和一个在第二个处理器访问之前执行的操作。不按照同步排序可能更新变量的情况被称为数据竞争,因为执行结果取决于处理器的相对速度,正如硬件设计中的竞赛,结果是不可预测的,这也导致了同步程序的另一种称呼:无数据竞争。

作为一个简单的例子,考虑一个变量被两个不同处理器读取和更新。每个处理器在读取和更新操作前后都使用锁和解锁,以确保更新的互斥性,并确保读取的一致性。显然,每次写入现在都由一对同步操作分隔开:一个解锁(在写入之后)和一个锁(在读取之前)。当然,如果两个处理器在没有插入读取的情况下同时写入一个变量,那么这些写入也必须由同步操作分隔开。

普遍接受的观察是,大多数程序都是同步的。这个观察主要是因为,如果访问是无序的,程序的行为可能会变得不可预测,因为执行速度将决定哪个处理器赢得数据竞争,从而影响程序的结果。即便是在顺序一致性下,推理这样的程序也是非常困难的。

程序员可以尝试通过构造自己的同步机制来保证排序,但这非常棘手,可能导致程序出现错误,并且可能在架构上不受支持,意味着它们可能无法在多处理器的未来版本中工作。因此,几乎所有程序员都会选择使用针对多处理器和特定同步类型进行了优化的正确的同步库。

最后,使用标准的同步原语确保即使架构实现的比顺序一致性更宽松的一致性模型,同步程序的行为也将如同硬件实现了顺序一致性一样。

### 放松一致性模型:基础与释放一致性

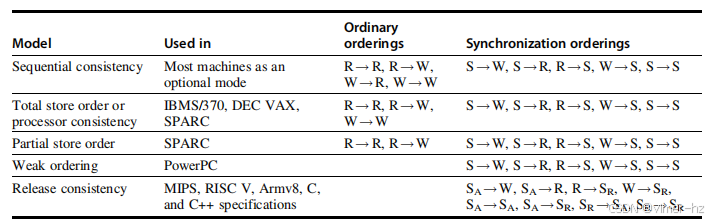

放松一致性模型的关键思想是允许读写操作以无序方式完成,但通过同步操作来强制执行顺序,使得同步程序的行为看起来就像处理器是顺序一致的一样。这些放松模型根据它们放松的读取和写入顺序进行分类。我们通过一组规则来指定顺序,形式为 X!Y,表示操作 X 必须在操作 Y 完成之前完成。顺序一致性要求维护所有四种可能的顺序:R!W、R!R、W!R 和 W!W。放松模型则由它们放松的四个顺序的子集定义:

1. 仅放松 W!R 顺序会产生一个称为总存储顺序或处理器一致性的模型。由于该模型保留了写入之间的顺序,许多在顺序一致性下运行的程序在这个模型下也能正常工作,而无需额外的同步。

2. 同时放松 W!R 顺序和 W!W 顺序会产生一个称为部分存储顺序的模型。

3. 放松所有四种顺序会产生包括弱顺序、PowerPC 一致性模型和释放一致性(RISC V 一致性模型)在内的多种模型。

通过放松这些顺序,处理器可以获得显著的性能优势,这也是 RISC V、ARMv8 以及 C++ 和 C 语言标准选择释放一致性作为模型的原因。

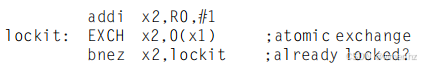

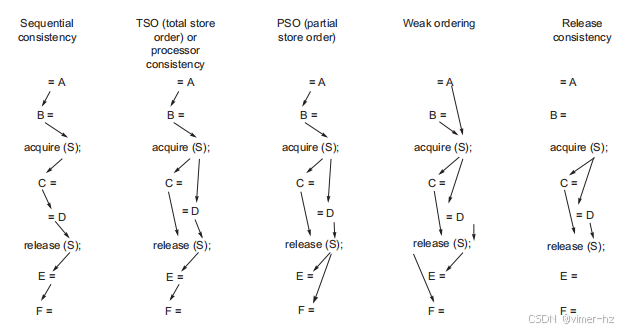

释放一致性区分用于获取对共享变量访问的同步操作(称为 SA)和用于释放对象以允许其他处理器获取访问权限的操作(称为 SR)。释放一致性基于这样的观察:在同步程序中,获取操作必须在使用共享数据之前,而释放操作必须在对共享数据的任何更新之后,并且还必须在下一次获取之前。这一属性使我们能够稍微放宽顺序,观察到在获取之前的读取或写入不必在获取之前完成,以及在释放之后的读取或写入不必等待释放。因此,保留下来的顺序仅涉及 SA 和 SR,如图 5.23 所示;如图 5.24 中的示例所示,该模型施加了五种模型中最少的顺序。

图 5.23 各种一致性模型对普通访问和同步访问施加的顺序关系如图所示。这些模型从最严格的(顺序一致性)到最宽松的(释放一致性)逐渐放宽,允许实现上的更大灵活性。较弱的模型依赖于由同步操作创建的屏障,而不是在每个内存操作中隐含的屏障。SA 和 SR 分别代表获取和释放操作,是定义释放一致性所必需的。如果我们在每个 S 中一致地使用 SA 和 SR 的符号,则每个带有一个 S 的顺序将变成两个顺序(例如,S!W 变为 SA!W 和 SR!W),而每个 S!S 将变为右下表格最后一行中显示的四个顺序。

图 5.24 本节讨论的五种一致性模型的示例展示了随着模型放松,施加的顺序数量的减少。仅显示了带箭头的最小顺序。由于传递性隐含的顺序,例如在顺序一致性模型中 C 的写入在 S 的释放之前,或在弱顺序或释放一致性中获取操作在释放之前的顺序,并未显示。

释放一致性提供了一种限制最少的模型,易于检查,并确保同步程序将看到顺序一致的执行。尽管大多数同步操作要么是获取操作,要么是释放操作(获取操作通常读取一个同步变量并原子性地更新它,而释放操作通常只是写入它),某些操作,例如屏障,既充当获取又充当释放,从而使顺序等价于弱顺序。虽然同步操作始终确保先前的写入已完成,但我们可能希望保证写入在没有明确同步操作的情况下完成。在这种情况下,使用一种称为 FENCE 的显式指令来确保该线程中的所有先前指令都已完成,包括所有内存写入和相关失效的完成。有关放松模型的复杂性、实现问题和性能潜力的更多信息,我们强烈推荐 Adve 和 Gharachorloo(1996)的优秀教程。

5.7 Cross-Cutting Issues

由于多处理器重新定义了许多系统特性(例如,性能评估、内存延迟和可扩展性的重要性),它们引入了有趣的设计问题,涉及硬件和软件的各个方面。在本节中,我们给出几个与内存一致性问题相关的示例。随后,我们将探讨在多线程添加到多处理时所获得的性能提升。

#### 编译器优化与一致性模型

定义内存一致性模型的另一个原因是指定对共享数据可以执行的合法编译器优化范围。在显式并行程序中,除非同步点明确且程序已同步,否则编译器不能互换两个不同共享数据项的读写,因为这样的转换可能会影响程序的语义。这一限制甚至阻止了相对简单的优化,例如共享数据的寄存器分配,因为这一过程通常涉及读写的互换。在隐式并行化程序中,例如使用高性能福特兰(HPF)编写的程序,程序必须是同步的,并且同步点是已知的,因此不会出现这个问题。编译器是否能够从更宽松的一致性模型中获得显著优势仍然是一个悬而未决的问题,既从研究角度看,也从实际应用角度看,缺乏统一模型可能会阻碍编译器的部署进展。

### 使用推测来隐藏严格一致性模型中的延迟

正如我们在第三章中所看到的,推测可以用来隐藏内存延迟。它也可以用来隐藏由于严格一致性模型而产生的延迟,从而带来许多放宽内存模型的好处。关键思想是处理器使用动态调度重新排序内存引用,从而让它们可能以无序的方式执行。以无序执行内存引用可能会导致顺序一致性的违规,这可能会影响程序的执行。通过利用推测处理器的延迟提交特性,可以避免这种可能性。假设一致性协议基于失效机制。如果处理器在内存引用提交之前接收到对该内存引用的失效,处理器将使用推测恢复机制撤销计算,并从被失效地址的内存引用重新开始。

如果处理器对内存请求的重新排序导致的执行顺序可能产生与顺序一致性下不同的结果,处理器将重新执行这一过程。使用这种方法的关键在于,处理器只需保证结果与所有访问按顺序完成时的结果相同,而它可以通过检测结果何时可能有所不同来实现。这种方法具有吸引力,因为推测重启几乎不会被触发。只有在存在未同步访问并且实际导致竞争条件时,才会触发重启(Gharachorloo et al., 1992)。

Hill(1998)提倡将顺序一致性或处理器一致性与推测执行相结合,作为首选的一致性模型。他的论点分为三部分。首先,顺序一致性或处理器一致性的激进实现将获得更放宽模型的大部分优势。其次,这种实现对推测处理器的实现成本增加非常有限。第三,这种方法允许程序员使用更简单的顺序或处理器一致性的编程模型进行推理。MIPS R10000设计团队在1990年代中期意识到了这一点,并利用R10000的乱序能力支持这种激进的顺序一致性实现。

一个悬而未决的问题是编译器技术在优化对共享变量的内存引用方面会有多成功。优化技术的现状以及共享数据通常通过指针或数组索引访问的事实限制了此类优化的使用。如果这种技术能够得到应用并带来显著的性能优势,编译器开发者将希望能够利用更放宽的编程模型。这个可能性以及对未来保持灵活性的渴望促使RISC V设计者在经过一系列长时间的辩论后选择了发布一致性。

### 包含性及其实现

所有多处理器系统都使用多级缓存层次结构,以减少对全局互连的需求以及缓存未命中的延迟。如果缓存还提供多级包含性——每一级缓存层次都是比其更远离处理器的层级的子集——那么我们可以利用这种多级结构来减少在监视和处理器缓存访问必须争用缓存时所产生的一致性流量与处理器流量之间的竞争。许多具有多级缓存的多处理器系统强制执行包含性属性,尽管最近一些具有较小L1缓存和不同块大小的多处理器有时选择不强制执行包含性。这种限制也称为子集属性,因为每个缓存都是其下方缓存的子集。

乍一看,保持多级包含性属性似乎是微不足道的。考虑一个两级示例:在L1中的任何未命中要么在L2中命中,要么在L2中生成未命中,从而导致数据被引入到L1和L2中。同样,在L2中命中的任何失效必须发送到L1,如果该块存在,则会导致其被失效。然而,当L1和L2的块大小不同时,会发生什么呢?

选择不同的块大小是相当合理的,因为L2将会大得多,并且在其未命中惩罚中具有更长的延迟成分,因此希望使用更大的块大小。当块大小不同的时候,我们的“自动”包含性强制执行会发生什么?L2中的一个块代表多个L1中的块,而L2中的未命中会导致替换相当于多个L1块的数据。例如,如果L2的块大小是L1的四倍,那么L2中的未命中将替换相当于四个L1块的数据。让我们考虑一个详细的例子。

**示例**

假设L2的块大小是L1的四倍。展示一个地址的未命中如何导致L1和L2中的替换,从而违反包含性属性。

**回答**

假设L1和L2都是直接映射缓存,L1的块大小为b字节,而L2的块大小为4b字节。假设L1包含两个块,其起始地址为x和x+b,并且x mod 4b = 0,这意味着x也是L2中一个块的起始地址;因此,L2中的这个单一块包含了L1块x、x+b、x+2b和x+3b。假设处理器生成了对块y的引用,该块在两个缓存中都映射到包含x的块,因此发生了未命中。

由于L2也未命中,它将提取4b字节并替换掉包含x、x+b、x+2b和x+3b的块,而L1则提取b字节并替换掉包含x的块。由于L1仍然包含x+b,但L2不再包含,因此包含性属性不再成立。

为了在多块大小下维护包含性,当在较低层级进行替换时,我们必须查询更高层级的缓存,以确保在较低层级替换的任何字节在更高层级的缓存中被失效;不同层级的关联性会产生类似的问题。Baer和Wang(1988)详细描述了包含性的优点和挑战,并且在2017年,大多数设计师选择实现包含性,通常通过在所有缓存级别上统一块大小来实现。例如,Intel i7使用了L3的包含性,这意味着L3始终包含所有L2和L1的内容。这一决定使得i7能够在L3实现简单的目录方案,并将来自于L1和L2的干扰最小化,仅在目录指示L1或L2有缓存副本的情况下进行干扰。

相对而言,AMD Opteron使L2包含L1,但对L3没有这样的限制。它使用了一种监听协议,但只有在L2发生命中时才需要监听L1。

### 性能提升来自多处理和多线程

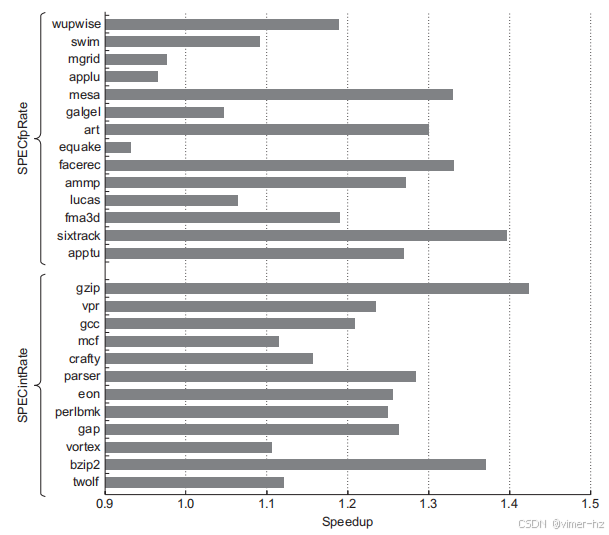

在本节中,我们简要探讨了一项关于在多核处理器(IBM Power5)上使用多线程的有效性研究;在下一节中,当我们检查英特尔i7的性能时,会再次回到这个话题。IBM Power5是一个支持同时多线程(SMT)的双核处理器;其基本架构与更近期的Power8(我们将在下一节中讨论)非常相似,但每个处理器只有两个核心。

为了考察多处理器中多线程的性能,研究人员在一台配备八个Power5处理器的IBM系统上进行了测量,每个处理器只使用一个核心。图5.25显示了8处理器Power5多处理器在有无同时多线程(SMT)情况下,对于SPECRate2000基准测试的加速比,如标题所述。平均而言,SPECintRate速度提升为1.23倍,SPECfpRate速度提升为1.16倍。需要注意的是,某些浮点基准测试在SMT模式下的性能略有下降,最大加速比降低至0.93。虽然人们可能会预期SMT能够更好地隐藏SPECFP基准测试较高的未命中率,但在此类基准下的SMT模式运行时,似乎遇到了内存系统的限制。

图5.25 在8处理器IBM eServer p5 575上,使用SPECfpRate(上半部分)和SPECintRate(下半部分)作为基准的SMT与单线程(ST)性能比较。注意,x轴从0.9的加速比开始,表示性能损失。每个Power5核心中只有一个处理器处于活动状态,这应该通过减少内存系统中的破坏性干扰来稍微改善SMT的结果。SMT结果是通过创建16个用户线程获得的,而ST结果仅使用八个线程;由于每个处理器仅有一个线程,Power5被操作系统切换到单线程模式。这些结果由IBM的John McCalpin收集。从数据可以看出,SPECfpRate的结果标准差高于SPECintRate(分别为0.13和0.07),这表明FP程序的SMT提升可能会有很大变化。

5.8 Putting It All Together: Multicore Processors and Their Performance

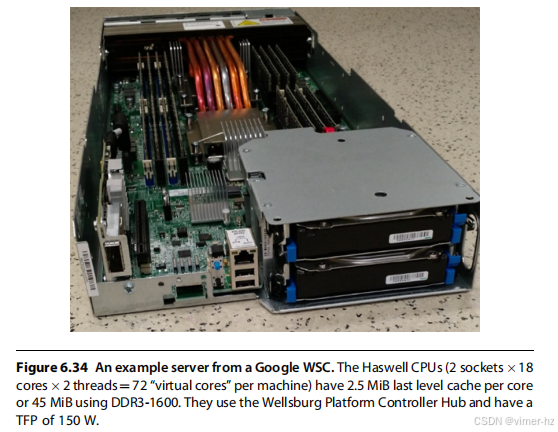

在大约10年的时间里,多核一直是提升性能的主要焦点,尽管其实现方式差异很大,对于更大规模的多芯片多处理器的支持也各不相同。在本节中,我们将研究三种不同多核的设计,它们对更大多处理器的支持以及一些性能特征,然后进行对小型到大型Xeon系统的更广泛评估,最后详细评估i7 920这一i7 6700的前身。

### 基于多核的多处理器在多程序工作负载下的性能

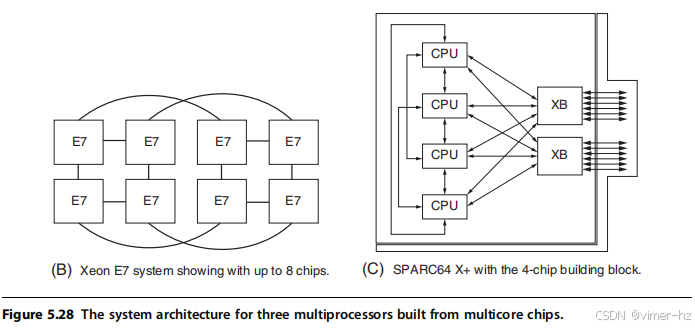

图5.26展示了三款为服务器应用设计的多核处理器的关键特性,这些处理器在2015至2017年间上市。Intel Xeon E7基于与i7相同的基本设计,但具有更多的核心、稍慢的时钟频率(功耗是限制因素)和更大的L3缓存。Power8是IBM Power系列中的最新款,拥有更多核心和更大的缓存。Fujitsu SPARC64 X+是最新的SPARC服务器芯片;与第三章提到的T系列不同,它采用了SMT。由于这些处理器被配置用于多核和多处理器服务器,因此它们作为一个家族提供,处理器数量、缓存大小等各不相同,如图所示。

图5.26 三款近期高端多核处理器(2015-2017年发布)的特性总结 该表展示了每个处理器系列中处理器数量、时钟频率和缓存大小的范围。Power8的L3采用非均匀缓存访问(NUCA)设计,并支持高达128 MiB的外部L4缓存,使用EDRAM技术。最近宣布了一款32核的Xeon处理器,但尚未有系统发货。Fujitsu SPARC64也提供8核设计,通常配置为单处理器系统。最后一行显示了具有已发布性能数据(如SPECintRate)的配置系统范围,其中包括处理器芯片数量和总核心数。Xeon系统包括通过额外逻辑扩展基本互连的多处理器;例如,使用标准的Quickpath互连将处理器数量限制为8,而最大系统为24个处理器(共192个核心),但SGI通过额外逻辑扩展互连(和一致性机制),提供了一个使用18核处理器芯片的32处理器系统,总规模为576个核心。这些处理器的新版本提高了时钟频率(在Power8的情况下显著,其他情况相对较少)和核心数量(在Xeon的情况下显著)。

这三种系统展示了连接片上核心和多个处理器芯片的一系列技术。首先,让我们看看核心在芯片内的连接方式。SPARC64 X+是最简单的:它在16个核心之间共享一个24路组相联的L2缓存。还有四个独立的DIMM通道,用于连接可通过一个16%的4开关访问的内存。

图5.27 显示了Power8和Xeon E7的芯片内部组织。Power8在L3缓存和CPU核心之间使用8条独立的总线。每个Power8还拥有两组链接,用于连接更大的多处理器系统。Xeon则使用三个环路连接处理器和L3缓存银行,并通过QPI进行芯片间链接。软件用于将一半的核心逻辑上关联到每个内存通道。

图5.27展示了Power8和Xeon E7芯片的组织结构。Power8中的每个核心都有一个直接连接的8 MiB L3缓存;其他缓存通过具有8条独立总线的互连网络访问。因此,Power8是真正的非均匀缓存架构(NUCA),因为访问所连接的L3缓存的时间要比访问其他L3缓存快得多。每个Power8芯片都有一组链接,可用于构建大型多处理器系统,我们很快会看到这种组织方式。内存链接连接到一个特殊的内存控制器,该控制器包括一个L4,并直接与DIMM接口。

图5.27 B部分展示了当Xeon E7处理器芯片中有18个或更多核心(该图显示20个核心)时的组织结构。

三个环路连接核心和L3缓存银行,每个核心和每个L3缓存银行都连接到两个环路。因此,任何缓存银行或核心都可以通过选择合适的环路从其他核心访问。因此,在芯片内部,E7具有均匀的访问时间。然而,在实际操作中,E7通常以NUMA架构运行,通过将一半核心逻辑上关联到每个内存通道来增加所需内存页在特定访问时可用的概率。E7提供3个QuickPath互连(QPI)链接,用于连接多个E7处理器。

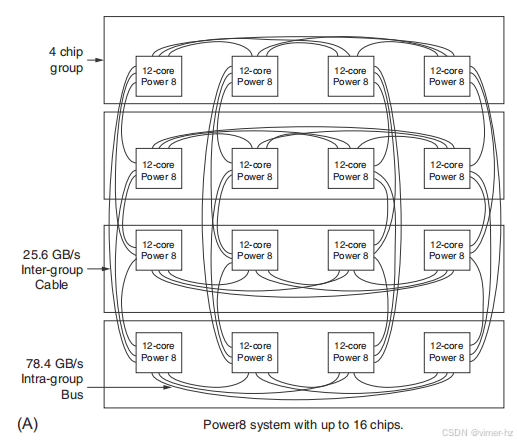

由这些多核处理器组成的多处理器系统使用多种不同的互连策略,如图5.28所示。Power8设计支持连接16个Power8芯片,总共192个核心。组内链接为完全连接的4个处理器芯片模块提供更高带宽的互连。组间链接用于将每个处理器芯片连接到其他3个模块。因此,每个处理器与任何其他处理器之间相距两跳,内存访问时间取决于地址是位于本地内存、集群内存还是跨集群内存(实际上后者可以有两个不同的值,但差异被跨集群时间所掩盖)。

Xeon E7使用QPI将多个多核心芯片互连。在一个由4个芯片组成的多处理器系统中,结合最新发布的Xeon,可以达到128个核心,每个处理器上的三个QPI链接与三个邻近处理器相连,从而形成一个4芯片完全连接的多处理器系统。由于内存直接连接到每个E7多核芯片,即使在这个4芯片的安排中,也存在非均匀内存访问时间(本地与远程)。图5.28展示了如何连接8个E7处理器;与Power8类似,这种连接方式使得每个处理器与其他处理器之间只需一到两跳。许多基于Xeon的多处理器服务器拥有超过8个处理器芯片。在这种设计中,典型的组织结构是将4个处理器芯片以方形模块连接在一起,每个处理器与两个邻居相连。每个芯片的第三个QPI连接到交叉开关。这种方式可以构建非常大的系统。内存访问可以发生在四个位置,具有不同的时延:处理器本地、立即邻居、距离两跳的集群邻居以及通过交叉开关访问。其他组织结构也是可能的,这样可以少用一个完整的交叉开关,以换取更多跳数来访问远程内存。

SPARC64 X+也使用4处理器模块,但每个处理器与其邻近的处理器有三个连接,以及两个(或在最大配置中三个)连接到交叉开关。在最大配置中,可以将64个处理器芯片连接到两个交叉开关,总共可达1024个核心。内存访问为NUMA(本地、模块内和通过交叉开关),一致性是基于目录的。

### 多核基础多处理器在多程序工作负载下的性能

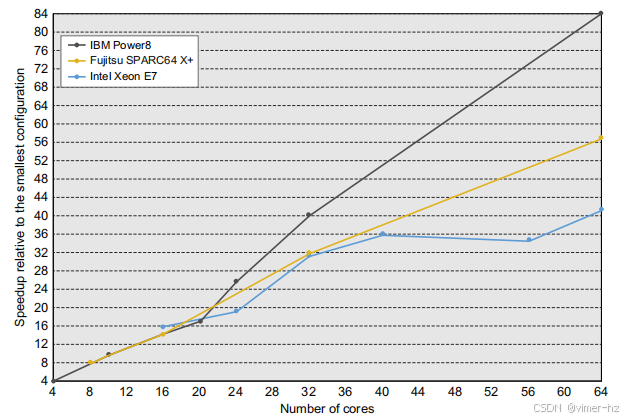

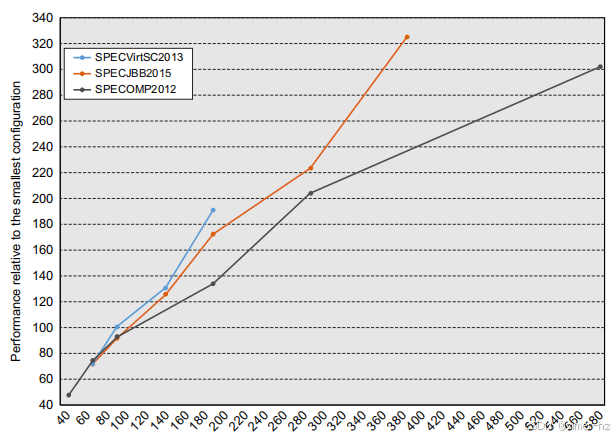

首先,我们使用SPECintRate比较这三款多核处理器的性能可扩展性,考虑最多64个核心的配置。图5.29展示了性能相对于最小配置的可扩展性,最小配置在4到16个核心之间变化。在图中,假设最小配置具有完美的加速(即8个核心为8,12个核心为12,等等)。该图并未显示不同处理器之间的性能对比。实际上,这些性能差异显著:在4核配置中,IBM Power8的每核心性能是SPARC64 X+的1.5倍!相反,图5.29展示了随着额外核心的增加,每个处理器系列的性能如何变化。

在这三款处理器中,有两款在扩展到64个核心时表现出收益递减的趋势。Xeon系统在56和64核心时似乎表现出最大的性能下降。这可能主要是因为更多核心共享较小的L3缓存。例如,40核系统使用4个芯片,每个芯片有60 MiB的L3缓存,这样每个核心分配到6 MiB的L3缓存。而56核和64核系统也使用4个芯片,但每个芯片只有35或45 MiB的L3缓存,导致每个核心只有2.5–2.8 MiB的L3缓存。结果,较大的L3未命中率可能导致56核和64核系统的加速性能下降。

图5.29 四款多核处理器在SPECintRate基准测试中的性能可扩展性 图5.29展示了当核心数量增加到64时,四款多核处理器在SPECintRate基准测试中的性能可扩展性。每个处理器的性能相对于最小配置进行绘制,并假设该配置具有完美的加速。尽管该图显示了特定多处理器在增加核心时的可扩展性,但并未提供不同处理器之间的性能数据。在同一处理器系列内部,时钟频率存在差异。这些差异通常被核心扩展效应所掩盖,除了Power8在从最小配置到64核配置时,其时钟频率范围变化为1.5%。

IBM Power8的结果也很不寻常,表现出显著的超线性加速。然而,这一效应主要是由于时钟频率的差异,在Power8处理器之间的差异远大于图中其他处理器。特别是,64核配置的时钟频率最高(4.4 GHz),而4核配置的时钟频率为3.0 GHz。如果我们根据与4核系统的时钟频率差异对64核系统的相对加速进行归一化,则有效加速为57,而不是84。因此,虽然Power8系统的可扩展性良好,可能在这些处理器中表现最佳,但并非奇迹。

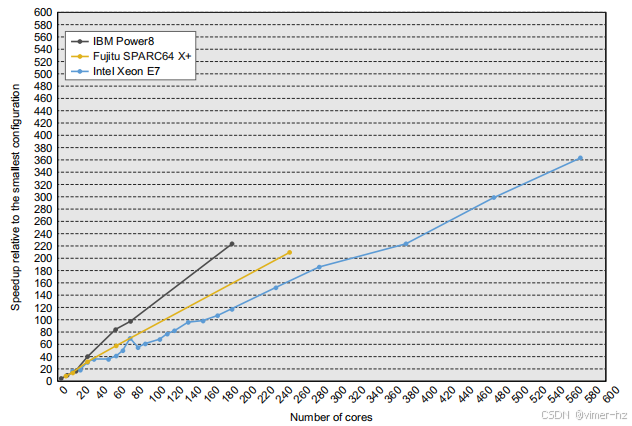

图5.30展示了这三款系统在超过64个处理器配置下的可扩展性。同样,时钟频率差异解释了Power8的结果;在192个处理器时,考虑到时钟频率差异后的等效加速为167,而未考虑时钟频率差异时为223。即使是167,Power8的可扩展性仍然优于SPARC64 X+或Xeon系统。令人惊讶的是,尽管从最小系统扩展到64核时,加速效果受到一些影响,但在这些更大配置下似乎并没有显著恶化。这种工作负载的特性高度并行且用户-CPU密集,而且在扩展到64核时所付出的开销可能导致了这一结果。

图5.30 多处理器多核的相对性能可扩展性。与之前一样,性能是相对于最小可用系统进行展示的。80核的Xeon结果与较小配置中出现的L3效应相同。所有大于80核的系统每个核心的L3缓存在2.5到3.8 MiB之间,而80核或更小的系统每个核心则有6 MiB的L3缓存。

### Xeon MP在不同工作负载下的可扩展性

在本节中,我们关注Xeon E7多处理器在三种不同工作负载下的可扩展性:基于Java的商业工作负载、虚拟机工作负载和科学并行处理工作负载,所有这些均来自SPEC基准测试组织,具体描述如下。

- **SPECjbb2015**:模拟一个超市IT系统,该系统处理混合的销售点请求、在线购买和数据挖掘操作。性能指标侧重于吞吐量,我们使用运行多个Java虚拟机的服务器端的最大性能测量。

- **SPECVirt2013**:模拟一组独立运行其他SPEC基准的虚拟机,包括CPU基准、Web服务器和邮件服务器。该系统必须为每个虚拟机满足服务质量保证。

- **SPECOMP2012**:由14个使用OpenMP标准编写的科学和工程程序组成,适用于共享内存的并行处理。这些代码使用Fortran、C和C++编写,涵盖从流体动力学到分子建模再到图像处理等多个领域。

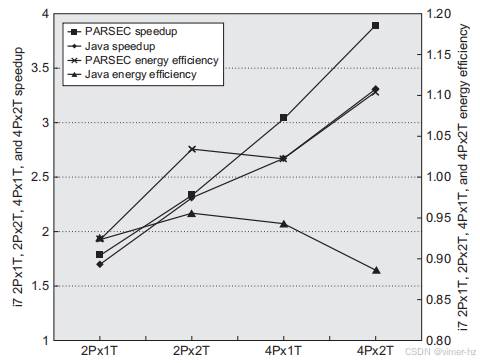

与之前的结果一样,图5.31显示了假设最小配置(对于这些基准测试,范围从48核到72核)线性加速的性能,并将性能相对于该最小配置进行绘制。SPECjbb2015和SPECVirt2013包括重要的系统软件,包括Java虚拟机软件和虚拟机监控程序。除了系统软件外,进程之间的交互非常小。相比之下,SPECOMP2012是一个真正的并行代码,多个用户进程共享数据并协作进行计算。

图5.31 展示了在一系列Xeon E7系统上的性能扩展,显示相对于最小基准配置的性能,并假设该配置获得完美的加速(例如,最小的SPECOMP配置为30个核心,我们假设该系统的性能为30)。从这些数据中只能评估相对性能,基准测试之间的比较没有相关性。请注意垂直轴和水平轴的比例差异。

让我们首先看看SPECjbb2015。它在最大的配置中获得了78%到95%之间的加速效率(加速/处理器比),显示出良好的加速性能。SPECVirt2013的表现更佳(在测量的系统范围内),在192核时几乎实现了线性加速。SPECjbb2015和SPECVirt2013都是随着系统规模增大而扩展应用程序大小的基准测试(如第1章讨论的TPC基准),因此阿姆达尔定律和进程间通信的影响较小。

最后,让我们来看SPECOMP2012,这是这些基准测试中计算密集度最高的一个,真正涉及并行处理。这里可见的主要趋势是,当我们从30个核心扩展到576个核心时,效率稳步下降,以至于在576个核心时,系统的效率仅为30个核心时的一半。这一效率降低导致相对加速比为284,假设30个核心时的加速比为30。这可能是由于有限的并行性以及同步和通信开销所导致的阿姆达尔定律效应。与SPECjbb2015和SPECVirt2013不同,这些基准测试并没有针对更大系统进行扩展。

**Intel i7 920多核处理器的性能与能效**

在本节中,我们仔细研究了i7 920的性能,作为6700的前身,我们关注了第三章中讨论的两组基准测试:并行Java基准和并行PARSEC基准(详细描述见247页的图3.32)。尽管本研究使用的是较旧的i7 920,但它仍然是关于多核处理器能效及多核与SMT结合效果的最全面研究。i7 920和6700的相似性表明,基本的洞察力也适用于6700。

首先,我们观察不使用SMT时多核性能与单核性能的扩展情况。接着,我们结合多核和SMT的能力。本节中的所有数据与早期的i7 SMT评估(第三章)相同,数据集与之前使用的一致(见247页的图3.32),只不过删除了Java基准中的tradebeans和pjbb2005(仅保留五个可扩展的Java基准);因为tradebeans和pjbb2005即使在四个核心和八个线程下也从未实现超过1.55的加速,因此不适合用于评估更多核心的性能。

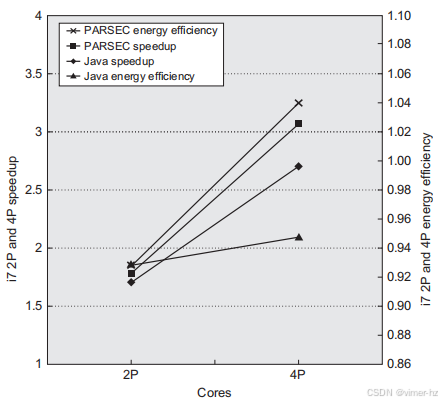

**图5.32** 此图显示了在不使用SMT的情况下,二核和四核执行并行Java和PARSEC工作负载的加速比和能效。这些数据由Esmaeilzadeh等人(2011年)收集,使用的是与第三章中描述的相同设置。Turbo Boost被关闭。加速比和能效使用调和平均数进行总结,意味着在2个核心上运行每个基准测试所花费的总时间是等效的。

图5.32绘制了Java和PARSEC基准在不使用SMT时的加速比和能效。能效通过以下比例计算:单核运行所消耗的能量除以双核或四核运行所消耗的能量(即,效率是能量消耗的倒数)。更高的能效意味着处理器在进行相同计算时消耗更少的能量,值为1.0时表示盈亏平衡点。在所有情况下,未使用的核心处于深度睡眠模式,这最大程度地降低了它们的功耗,基本上将其关闭。在比较单核和多核基准的数据时,重要的是要记住,在单核(以及多核)情况下,L3缓存和内存接口的全部能量成本都是要支付的。这一事实增加了对于合理扩展的应用程序,能量消耗改善的可能性。调和平均数用于总结结果,并在说明中做出相关解释。

如图所示,PARSEC基准测试的加速比优于Java基准测试,在四核上实现了76%的加速效率(即,实际加速除以处理器数量),而Java基准测试在四核上实现了67%的加速效率。尽管这一观察从数据中显而易见,但分析为何存在这种差异是困难的。很可能是因为Amdahl法则的影响,降低了Java工作负载的加速比,因为它包含一些典型的串行部分,例如垃圾回收器。此外,处理器架构与应用程序之间的交互也可能发挥作用,这会影响同步或通信成本等问题。特别是,像PARSEC中的一些良好并行化的应用程序,有时会受益于计算与通信之间的有利比例,从而减少对通信成本的依赖(见附录I)。

这些加速差异转化为能效差异。例如,PARSEC基准测试的能效实际上比单核版本略有改善;这个结果可能受益于L3缓存在多核运行中比在单核情况下更有效地使用,而在两种情况下的能量成本是相同的。因此,对于PARSEC基准测试,多核方法实现了设计者在从ILP聚焦设计转向多核设计时所希望的目标;即,它的性能扩展速度与功耗扩展一样快,甚至更快,从而实现恒定或甚至改善的能效。在Java的情况下,我们看到无论是二核还是四核运行都未能实现能效的盈亏平衡,因为Java工作负载的加速水平较低(尽管2p运行的Java能效与PARSEC相同)。四核Java案例中的能效相当高(0.94)。很可能,专注于ILP的处理器需要更多的功率,以在PARSEC或Java工作负载上实现可比的加速。因此,TLP中心的方法在提高这些应用程序的性能方面显然优于ILP中心的方法。正如我们将在5.10节中看到的,对于多核的简单、高效和长期扩展,仍然有理由持悲观态度。

### 将多核和超线程结合起来

最后,我们考虑通过对两个到四个处理器和一个到两个线程的两组基准测试进行测量,来研究多核和多线程的结合(总共四个数据点,最多八个线程)。图5.33展示了在Intel i7处理器上,当处理器数量为二或四且是否使用超线程时所获得的加速比和能效,使用调和平均数来总结这两组基准测试。显然,当存在足够的线程级并行性时,即使在多核情况下,超线程也可以提升性能。例如,在四核无超线程的情况下,Java和PARSEC的加速效率分别为67%和76%。而在四核启用超线程的情况下,这些比率则惊人地达到了83%和97%。

图5.33 该图展示了在启用和禁用超线程的情况下,双核和四核并行执行Java和PARSEC工作负载的加速比。请记住,之前的结果在线程数量上从两个到八个变化,并反映了架构效应和应用特性。正如图5.32的说明中所讨论的,使用调和平均数来总结结果。

能效呈现出略微不同的情况。在PARSEC的情况下,四核超线程(八个线程)的加速几乎是线性的,而功耗的增加速度更慢,导致该情况下的能效为1.1。Java的情况则更加复杂;在两核超线程(四个线程)运行时,能效达到峰值0.97,而在四核超线程(八个线程)运行时降至0.89。这表明,当部署超过四个线程时,Java基准测试很可能遇到了阿姆达尔定律的影响。正如一些架构师所观察到的,多核确实将更多的性能(因此也是能效)的责任转移给了程序员,而Java工作负载的结果无疑证明了这一点。

5.9 Fallacies and Pitfalls

鉴于我们对并行计算理解的不足,存在许多隐藏的陷阱,这些陷阱可能会被细心的设计师发现,也可能会让不幸的设计者遭遇麻烦。考虑到多处理器技术多年来所伴随的大量炒作,常见的误区层出不穷。我们在此列出了一些典型的误区。

陷阱 通过线性加速比与执行时间来衡量多处理器的性能。

像图5.32和图5.33那样绘制性能与处理器数量关系的图表,显示线性加速、平稳期以及随后下降,长期以来一直被用来评估并行处理器的成功。尽管加速比是并行程序的一个方面,但它并不是性能的直接衡量标准。首要问题在于所使用处理器的性能范围:一个线性提高性能以达到相当于100个Intel Atom处理器(用于上网本的低端处理器)的程序,可能比在8核Xeon上运行的版本还要慢。对于浮点密集型程序尤其要小心;没有硬件支持的处理单元可能在扩展时表现良好,但整体性能却较差。

仅当你比较每台计算机上最佳算法时,比较执行时间才算公平。在两台计算机上比较相同的代码似乎是公平的,但实际上并非如此;并行程序在单处理器上的运行速度可能比顺序版本更慢。开发并行程序有时会导致算法的改进,因此将之前已知的最佳顺序程序与并行代码进行比较——这看似公平——但并不能比较等效算法。为了解决这个问题,有时使用“相对加速比”(相同程序)和“真实加速比”(最佳程序)这两个术语。

结果如果显示出超线性性能,即在n个处理器上运行的程序比等效的单处理器快超过n倍,这可能表明比较是不公平的,尽管也有一些情况下确实遇到过“真实”的超线性加速。例如,一些科学应用在处理器数量从2或4增至8或16时,通常会实现超线性加速。这些结果通常是因为在2或4个处理器的多处理器系统中不适合进入的关键数据结构,能够适配8或16个处理器的汇总缓存。正如我们在前一部分看到的,其他差异(比如高时钟频率)在比较略有不同的系统时也可能表现出超线性加速。

总之,通过比较加速比来评估性能至多是棘手的,至于误导则更为严重。比较两种不同多处理器的加速比并不一定能告诉我们这些多处理器的相对性能,正如我们在前一部分所看到的。即使是在同一多处理器上比较两种不同的算法也是棘手的,因为我们必须使用真实加速比,而不是相对加速比,以获得有效的比较。

### 谬论:阿姆达尔定律不适用于并行计算机

1987年,一家研究机构的负责人声称,MIMD多处理器打破了阿姆达尔定律。然而,这并不意味着该定律已被并行计算机推翻;程序中被忽略的部分仍然会限制性能。为了理解媒体报道的基础,我们来看一下阿姆达尔(1967年)最初所说的话:

“此时可以得出一个相当明显的结论:除非在顺序处理速率上取得几乎相同量级的成就,否则为实现高并行处理速率所付出的努力是浪费。” [第483页]

对该定律的一种解释是,由于每个程序的某些部分必须是顺序执行的,因此有效的经济处理器数量是有限的——比如说100个。通过展示1000个处理器的线性加速,这种对阿姆达尔定律的解释被证伪。

声明阿姆达尔定律已被“克服”的依据是使用了规模加速,也称为弱扩展。研究人员将基准测试的 数据集规模扩大到1000倍,并比较了单处理器和并行执行的时间。对于这个特定算法,程序的顺序部分在输入大小独立时是恒定的,其余部分则是完全并行的——因此,在1000个处理器上实现了线性加速。然而,由于运行时间的增长速度超过了线性,即使在有1000个处理器的情况下,经过缩放后程序的运行时间实际上也变得更长。

假设输入规模扩展的加速与真正的加速并不相同,将其报告为相同是具有误导性的。由于并行基准测试通常在不同规模的多处理器上运行,因此重要的是要明确允许什么类型的应用扩展,以及如何进行这种扩展。虽然简单地根据处理器数量扩展数据大小很少合适,但对更大处理器数量假设固定问题大小(称为强扩展)往往也不合适,因为用户在面对更大的多处理器时很可能会选择运行更大或更详细的应用版本。有关这一重要主题的更多讨论,请参见附录I。

### 谬论:线性加速是实现多处理器成本效益的必要条件

人们普遍认为,并行计算的主要优点之一是提供比最快的单处理器更短的解决时间。然而,许多人也认为,除非并行处理器能够实现完美的线性加速,否则它们无法与单处理器在成本效益上相提并论。这个论点认为,由于多处理器的成本是处理器数量的线性函数,任何低于线性加速的表现都会导致性能/成本比下降,从而使并行处理器的成本效益低于单处理器。

这个论点的问题在于,成本不仅仅是处理器数量的函数,还取决于内存、输入/输出以及系统的开销(机箱、电源、互连等)。在多核时代,这种观点更显得不合理,因为每个芯片上都有多个处理器。

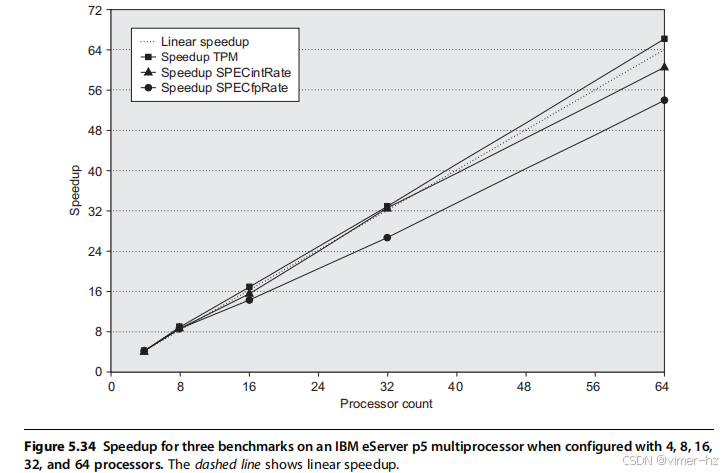

Wood和Hill(1995)指出了将内存纳入系统成本的影响。我们使用基于最新数据的TPC-C和SPECRate基准测试的例子来说明这一点,但同样的论点也适用于并行科学应用工作负载,这可能会使案例更为有力。

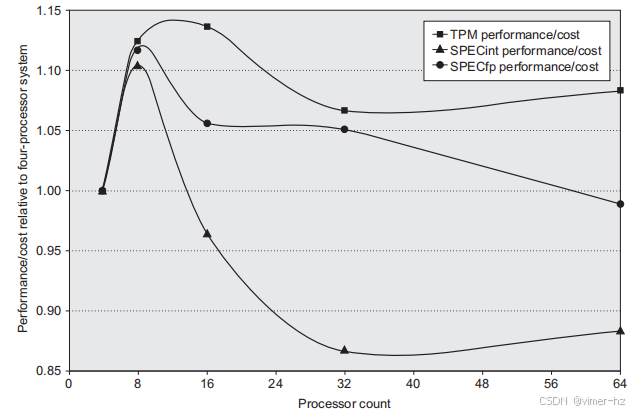

图5.34显示了在配置了4至64个处理器的IBM eServer p5多处理器上TPC-C、SPECintRate和SPECfpRate的加速比。图中显示,只有TPC-C的加速比优于线性加速。对于SPECintRate和SPECfpRate,加速比低于线性,但成本也是如此,因为与TPC-C不同,所需的主内存和磁盘容量的增长都低于线性。如图5.35所示,处理器数量更大的配置实际上可能比4处理器配置更具成本效益。在比较两台计算机的成本效益时,我们必须确保包括对总系统成本和可实现性能的准确评估。对于许多内存需求较大的应用程序来说,这样的比较可以极大地提高使用多处理器的吸引力。

图5.35显示了IBM eServer p5多处理器系统在4至64个处理器之间的性能/成本表现,相对于4处理器配置。任何高于1.0的测量结果都表明该配置比4处理器系统更具成本效益。对于所有三个基准测试,8处理器配置都显示出优势,而三个基准测试中的两个显示16处理器和32处理器配置在成本性能方面具有优势。对于TPC-C,这些配置是官方运行中使用的配置,这意味着随着处理器数量的增加,磁盘和内存的扩展几乎呈线性增长,64处理器机器的成本大约是32处理器版本的两倍。相比之下,磁盘和内存的扩展速度较慢(尽管仍然比在64处理器上实现最佳SPECrate所需的速度要快)。在……方面

特别是,磁盘配置从4处理器版本的1个驱动器增加到64处理器版本的4个驱动器(每个驱动器140GB)。内存从4处理器系统的8GB增加到64处理器系统的20GB。

陷阱 没有针对或优化多处理器体系结构开发软件。

在多处理器领域,软件一直落后于硬件,这可能是因为软件问题更加复杂。我们举一个例子来说明这个问题的微妙之处,但还有很多例子可以选择。

一个常见的问题是将为单处理器设计的软件移植到多处理器环境中。例如,2000年的SGI操作系统最初使用单个锁来保护页表数据结构,因为它假设页分配不频繁。在单处理器环境中,这并不构成性能问题。但在多处理器环境中,对于某些程序而言,它可能会成为主要的性能瓶颈。

考虑一个在启动时分配大量页面的程序,UNIX会为静态分配的页面使用页表数据结构。假设该程序被并行化,多个进程分配页面。因为每当页表数据结构被使用时,都会锁定它,所以即使操作系统允许多个线程同时运行,也会被序列化。这些进程都试图同时为其页面分配内存(这正是我们在初始化时所期望的)。

本页表序列化消除了初始化过程中的并行性,并对整体并行性能产生了显著影响。即使在多任务环境下,这种性能瓶颈也依然存在。例如,假设我们将并行程序分割成独立的进程,并在每个处理器上运行一个进程,以避免进程之间的共享(这正是一位用户所做的,因为他合理地认为性能问题源于他应用程序中的无意共享或干扰)。不幸的是,锁仍然会将所有进程序列化,因此即使在多任务环境下的性能也很差。这个陷阱表明,当软件在多处理器上运行时,可能会出现一些微妙但显著的性能问题。像许多其他关键软件组件一样,操作系统算法和数据结构必须在多处理器环境中重新考虑。将锁放置在页表的较小部分上可以有效地消除这个问题。在没有实际共享的情况下,内存结构中也存在类似的问题,这会增加一致性通信量。随着多核成为从台式机到服务器等各种设备的主导主题,这些问题变得越来越重要。在服务器领域,对并行软件的不足投资变得显而易见。由于缺乏关注,我们可能需要很多年才能充分利用日益增多的处理器核心。

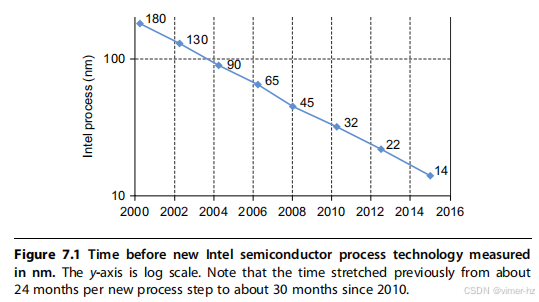

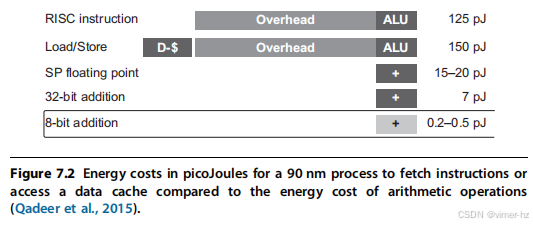

5.10 The Future of Multicore Scaling

在过去的30多年里,研究人员和设计师一直预测单处理器的终结以及多处理器的主导地位。直到本世纪初,这一预测一直被不断证伪。正如我们在第三章中看到的,寻找和利用更多指令级并行性(ILP)的成本在效率上变得不可承受(无论是在硅面积还是功率方面)。当然,多核并不能神奇地解决功率问题,因为它显然增加了晶体管数量和切换的活跃晶体管数量,这两者都是功率的主要贡献因素。正如我们将在本节中看到的,能源问题可能会比之前认为的更严重地限制多核扩展。

ILP扩展失败是由于可用ILP的限制以及利用这些ILP的效率。同样,两种因素的结合意味着通过增加核心简单地扩展性能不太可能广泛成功。这种结合源于阿姆达尔法则带来的挑战,该法则评估了利用并行性的效率,以及丹纳德缩放的终止,后者决定了多核处理器所需的能量。

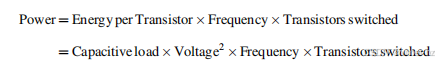

为了理解这些因素,我们采用一个简单的技术缩放模型(基于Esmaeilzadeh等人(2012)中的广泛且高度详细的分析)。让我们先回顾一下CMOS中的能量消耗和功率。回想一下第一章,切换一个晶体管所需的能量为:

![]()

CMOS缩放的限制主要是由热功率决定的,热功率是静态泄漏功率和动态功率的结合,后者往往占主导地位。功率的计算公式为:

为了理解能量和功率缩放的影响,我们将今天的22纳米技术与预计在2021-2024年可用的技术进行比较(具体取决于摩尔定律放缓的速度)。图5.36展示了基于技术预测及其对能量和功率缩放影响的比较。注意,功率缩放大于1.0意味着未来设备消耗更多功率;在这种情况下,为1.79倍。

图5.36 比较了2016年的22纳米技术与预计在2022年至2024年之间可用的未来11纳米技术。11纳米技术的特性基于国际半导体技术路线图,该路线图最近因摩尔定律的延续性及其缩放特性的不确定性而停止更新。

考虑一下这对最新的Intel Xeon处理器E7-8890的影响,该处理器具有24个核心,72亿个晶体管(包括近70 MiB的缓存),工作频率为2.2 GHz,热功率额定值为165瓦,芯片面积为456 mm²。时钟频率已经受到功率消耗的限制:4核版本的时钟为3.2 GHz,10核版本的时钟为2.8 GHz。使用11纳米技术,相同大小的芯片将容纳96个核心,几乎有280 MiB的缓存,并以4.9 GHz的时钟频率运行(假设完美的频率缩放)。不幸的是,在所有核心都运行且没有效率改善的情况下,它将消耗165%的1.79,即295瓦。如果我们假设165瓦的热失效限制保持不变,那么最多只能激活54个核心。这个限制在5到6年的时间跨度内实现的最大性能提升为54/24=2.25,低于1990年代末看到的性能缩放的一半。此外,正如下一个例子所示,我们可能还会遇到阿姆达尔法则的影响。

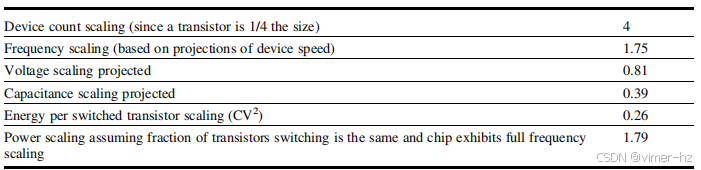

例子 假设我们有一个96核的未来一代处理器,但平均只有54个核心可以被忙用。假设90%的时间,我们可以使用所有可用的核心;9%的时间,我们可以使用50个核心;1%的时间是严格的串行执行。我们可以期待多大的加速?假设在不使用时核心可以关闭,不消耗电力,并且假设不同数量的核心的使用是分布式的,因此我们只需关注平均功耗。多核加速与99%时间可以使用所有处理器的24核版本相比如何?

回答 我们可以找出在90%时间内,当可用核心超过54个时,可以使用多少个核心,如下所示:

在考虑功率限制和阿姆达尔法则效应时,96核版本的加速效果不到24核版本的两倍。实际上,时钟频率的提升所带来的加速几乎与4%处理器数量增加所带来的加速相匹配。我们将在结论部分进一步讨论这些问题。

5.11 Concluding Remarks

在前一节中我们看到,多核并不能神奇地解决功率问题,因为它明显增加了晶体管数量和活动晶体管的切换数量,这两者是功率的主要来源。丹纳德缩放的失效使得这一情况更加极端。

然而,多核确实改变了游戏规则。通过将空闲核心置于省电模式,可以实现一定的功率效率改进,本章的结果显示了这一点。例如,在Intel i7中关闭某些核心可以让其他核心在Turbo模式下运行。这种能力允许在更高时钟频率与更少处理器之间,以及更多处理器与较低时钟频率之间进行权衡。

更重要的是,多核通过更多依赖线程级并行性(TLP)来转移保持处理器忙碌的负担,而TLP是应用程序和程序员负责识别的,反之指令级并行性(ILP)则由硬件负责。避免阿姆达尔法则效应的多程序和高度并行工作负载会更容易受益。

尽管多核在能源效率挑战上提供了一些帮助,并将很多负担转移到软件系统上,但仍然存在困难的挑战和未解决的问题。例如,利用线程级版本的激进猜测的尝试迄今为止遇到了与ILP相似的命运。也就是说,性能提升有限,可能还不及能耗的增长,因此诸如猜测线程或硬件提前执行等理念尚未成功融入处理器中。与ILP的猜测一样,除非猜测几乎总是正确,否则成本超过收益。

因此,目前看来,某种形式的简单多核扩展不太可能提供一种具有成本效益的性能增长路径。必须克服一个基本问题:以节能和硅高效的方式找到并利用大量的并行性。在前一章中,我们考察了通过SIMD方法利用数据并行性。在许多应用中,数据并行性大规模存在,SIMD是一种更具能效的数据并行性利用方法。在下一章中,我们探讨大规模云计算。在这样的环境中,来自个别用户的数百万个独立任务提供了大量的并行性。阿姆达尔法则对这些系统的规模限制作用微乎其微,因为任务(例如,数百万个谷歌搜索请求)是独立的。最后,在第七章中,我们探讨了领域特定架构(DSA)的兴起。大多数领域特定架构利用目标领域的并行性,通常是数据并行性,正如GPU一样,DSA在能源消耗或硅利用率方面能够实现更高的效率。

在2012年发布的最后一版中,我们提出了考虑异构处理器是否值得的问题。当时,没有这种多核处理器被交付或宣布,异构多处理器仅在专用计算机或嵌入式系统中取得有限成功。尽管编程模型和软件系统仍然具有挑战性,但异构处理器的多处理器不可避免地将在未来发挥重要作用。将领域特定处理器(如第四章和第七章讨论的处理器)与通用处理器结合,或许是实现性能和能效提升,同时保持通用处理器所提供的一部分灵活性的最佳途径。

6 Warehouse-Scale Computers to Exploit Request-Level and Data-Level Parallelism

数据中心就是计算机。

—— Luiz Andre Barroso, Google (2007)

一百年前,公司们停止使用蒸汽机和发电机自给自足,转而接入新建的电网。电力公司提供的廉价电力不仅改变了商业运作方式,还引发了一系列经济和社会变革,造就了现代世界。如今,一场类似的革命正在进行中。连接到互联网全球计算网络的大型信息处理中心开始将数据和软件代码源源不断地输送到我们的家庭和企业。这一次,计算正在变成一种公用事业。

—— Nicholas Carr,《大切换:从爱迪生到谷歌的全球重构》(2008)

6.1 Introduction

任何人都可以打造一款快速的 CPU,关键在于构建一个快速的系统。

—— Seymour Cray,被认为是超级计算机之父

仓库级计算机(WSC)是数十亿人每天使用的互联网服务的基础:搜索、社交网络、在线地图、视频分享、在线购物、电子邮件服务等等。这些互联网服务的巨大普及催生了能够满足公众快速需求的 WSC。尽管 WSC 表面上看似大型数据中心,但它们的架构和运作却截然不同,正如我们将要看到的。如今的 WSC 作为一台巨大的机器,建设成本高达数亿美元,涵盖电力和冷却基础设施、服务器以及连接和容纳 5 万到 10 万台服务器的网络设备。此外,商业云计算的快速增长(见第 6.5 节)使得任何持有信用卡的人都能使用 WSC。

计算机架构自然延伸到 WSC 的设计。例如,谷歌的 Luiz Barroso(前文引用)在计算机架构方面进行了博士论文研究。他认为,设计规模、确保可靠性以及调试硬件的能力对 WSC 的创建和运作非常有帮助。

在这个需要创新的前沿规模中,涉及电力分配、冷却、监控和运营等方面,WSC 是现代超级计算机的后代——这使得 Seymour Cray 成为当今 WSC 架构师的教父。他的极端计算机处理的是其他地方无法完成的计算,但由于成本极高,只有少数公司能够负担得起。这一次,目标是为世界提供信息技术,而不是为科学家和工程师提供高性能计算(HPC);因此,WSC 在当今社会中无疑比 Cray 的超级计算机在过去所起的作用更为重要。

毫无疑问,WSC 的用户数量比高性能计算多出几个数量级,并且它们在 IT 市场中占据了更大的份额。无论是从用户数量还是收入来看,谷歌的规模都是 Cray Research 的 1000 倍。

WSC 架构师与服务器架构师有许多共同的目标和要求:

- **成本效益**——每美元所完成的工作至关重要,这在很大程度上是由于规模的原因。将一组 WSC 的成本降低几个百分点可能节省数百万美元。

- **能效**——除了从 WSC 中释放出的光子外,它们本质上是封闭系统,几乎所有消耗的能量都转化为必须移除的热量。因此,峰值功率和实际消耗的电力影响着电力分配和冷却系统的成本。构建 WSC 的基础设施成本的主要部分用于电力和冷却。此外,能效也是环境管理的重要组成部分。因此,每焦耳所完成的工作对 WSC 及其服务器来说至关重要,因为构建计算机仓库的电力和机械基础设施的高成本以及随之而来的每月公用事业账单。

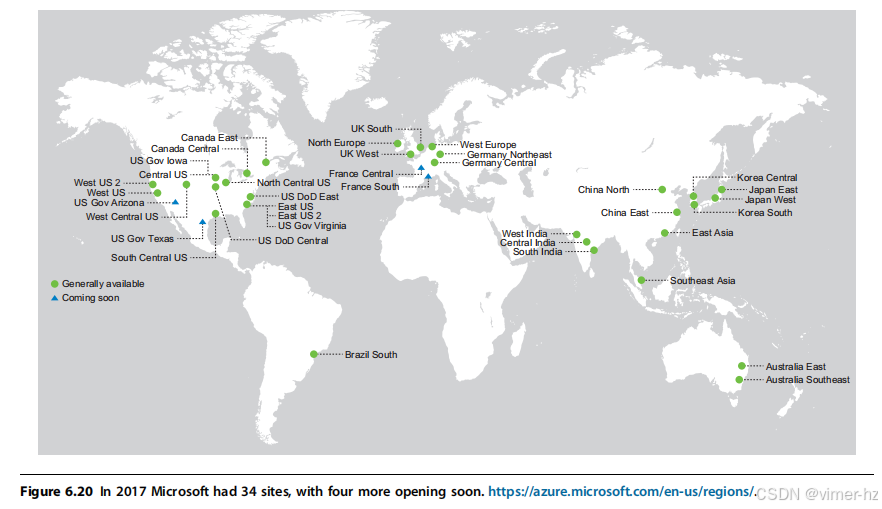

- **通过冗余确保可靠性**——互联网服务的长期运行性质意味着 WSC 中的硬件和软件必须共同提供至少 99.99%(称为“四个九”)的可用性;也就是说,服务每年停机时间必须少于 1 小时。冗余是确保 WSC 和服务器可靠性的关键。尽管服务器架构师通常会利用更多硬件以更高成本实现高可用性,但 WSC 架构师则依赖数量众多且具成本效益的服务器,通过网络连接并由软件管理冗余。除了 WSC 内部的本地冗余外,组织还需要冗余的 WSC 来掩盖可能导致整个 WSC 停机的事件。实际上,虽然每个云服务的可用性需求至少为 99.99%,但像亚马逊、谷歌或微软这样的完整互联网公司的可靠性需求甚至更高。如果这些公司中的任何一个每年完全离线 1 小时,即 99.99% 的可用性,那将成为头条新闻。多个 WSC 还有额外的好处,能够降低广泛部署服务的延迟(见图 6.18–6.20)。

- **网络 I/O**——服务器架构师必须为外部世界提供良好的网络接口,WSC 架构师也必须如此。网络连接是保持多个 WSC 之间数据一致性以及与公众接口所必需的。

- **交互式和批处理工作负载**——虽然对于拥有数十亿用户的搜索和社交网络等服务,预期会有高度交互式的工作负载,但 WSC 与服务器一样,也运行大规模并行批处理程序,以计算对这些服务有用的元数据。例如,运行 MapReduce 作业将从网络爬虫返回的页面转换为搜索索引(见第 6.2 节)。

不出所料,WSC(大规模计算中心)架构与服务器架构之间也存在一些不同的特征:

- **充足的并行性**——服务器架构师关心的是目标市场中的应用程序是否有足够的并发性来证明大量并行硬件的合理性,以及是否需要高昂的通信硬件成本来利用这种并行性。而 WSC 架构师则没有这样的顾虑。首先,批处理应用程序受益于大量独立的数据集,这些数据集需要独立处理,例如来自网络爬虫的数十亿个网页。这种处理属于数据级并行性,我们在第四章中见过,这次是应用于存储中的数据,而不是内存中的数据。其次,交互式互联网服务应用程序(也称为软件即服务,SaaS)可以从数百万个独立用户的交互式互联网服务中受益。在 SaaS 中,读写操作通常不相互依赖,因此很少需要同步。例如,搜索使用只读索引,而电子邮件通常读取和写入独立的信息。我们将这种易于实现的并行性称为请求级并行性,因为许多独立的操作可以自然地并行进行,几乎不需要通信或同步;例如,基于日志的更新可以减少吞吐量需求。即使是读/写依赖的特性,有时也会被放弃,以提供能够扩展到现代 WSC 尺寸的存储。在任何情况下,WSC 应用程序别无选择,只能找到能够在数百到数千台服务器上扩展的算法,因为这正是客户的期望,也是 WSC 技术所提供的。

- **运营成本重要**——服务器架构师通常忽视服务器的运营成本,认为与购买成本相比,这些成本微不足道。而 WSC 的使用寿命更长——建筑、电力和冷却基础设施通常要摊销 10 到 15 年——因此运营成本不断增加:能源、配电和冷却在 10 年内占 WSC 成本的 30%以上。

- **选址重要**——建设 WSC 的第一步是建立一个仓库。一个问题是在哪里?房地产经纪人强调位置,但 WSC 的位置意味着需接入水源、便宜的电力、靠近互联网主干光缆、有附近的人来工作,以及低风险的环境灾害(如地震、洪水和飓风)。更明显的关注点是土地成本,包括足够的空间来扩展 WSC。对于拥有多个 WSC 的公司,另一个关注点是寻找地理上靠近当前或未来互联网用户群体的地方,以减少互联网延迟。其他因素包括税收、物业成本、社会问题(人们有时希望在自己的国家设立设施)、政治问题(某些司法管辖区要求本地托管)、网络成本、网络可靠性、能源成本、能源来源(例如,水电与煤电)、天气(较凉爽的地区成本更低,如第 6.4 节所示)以及整体互联网连接性(澳大利亚地理上接近新加坡,但两者之间的网络链接带宽并不理想)。

- **低利用率下高效计算**——服务器架构师通常在成本预算内设计系统以达到峰值性能,并仅担心电力,以确保不超过其机箱的冷却能力。如我们所见(图 6.3),WSC 服务器很少能够完全利用,部分原因是为了确保低响应时间,部分原因是提供所需的冗余以实现可靠计算。鉴于运营成本的重要性,这些服务器在所有利用率水平上都需要高效计算。

■ 规模及其相关的机会/问题——极端计算机通常非常昂贵,因为它们需要定制硬件,而由于极端计算机的生产数量较少,定制成本无法有效摊销。然而,当一次购买数千台服务器时,可以享受巨大的批量折扣。WSC(大规模计算中心)内部规模庞大,即使WSC的数量不多,仍然存在规模经济。正如我们在第6.5节和第6.10节中将看到的,这些规模经济导致了商业云计算的出现,因为WSC的单位成本较低,使得公司能够以低于外部人士自行租用服务器的成本进行租赁。10万台服务器的另一面是故障。

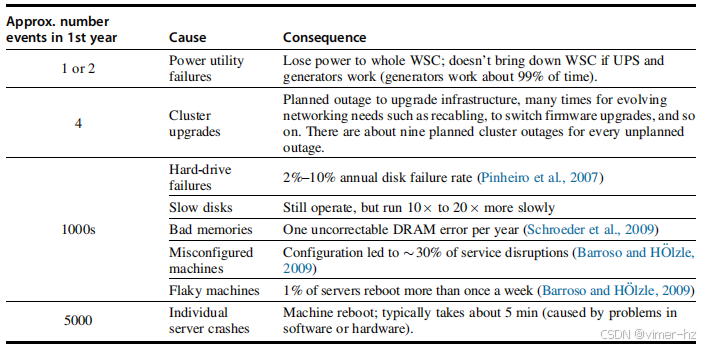

图6.1 列出了一个新集群(2400台服务器)第一年内的停机和异常情况及其大致发生频率。我们将Google所称的集群标记为阵列;参见图6.5。数据来源于Barroso, L.A. (2010) 的《仓库规模计算》[主题演讲],发表于2010年6月8日至10日的ACM SIGMOD会议,印第安纳波利斯,印第安纳州。

图6.1显示了2400台服务器的停机和异常情况。即使一台服务器的平均故障时间(MTTF)达到惊人的25年(200,000小时),WSC架构师仍需设计以应对每天五次服务器故障。图6.1列出了年化磁盘故障率为2%到10%。考虑到每台服务器有两个磁盘,年故障率为4%,在10万台服务器的情况下,WSC架构师应该预计每小时会发生一次磁盘故障。然而,软件故障远远超过硬件故障,如图6.1所示,因此系统设计必须具备抵御因软件错误导致的服务器崩溃的能力,这种崩溃发生的频率甚至高于磁盘故障。在这些大型设施中拥有数千台服务器后,WSC运营商在更换磁盘方面变得非常熟练,因此WSC的磁盘故障成本远低于小型数据中心。同样的道理也适用于DRAM。如果有更便宜的组件可用,WSC可能会使用更不可靠的组件。

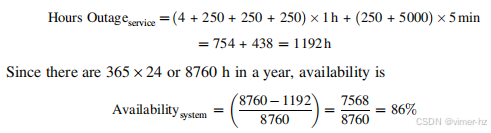

### 示例

计算图6.1中2400台服务器上运行的服务的可用性。与真实的WSC中的服务不同,在此示例中,该服务无法容忍硬件或软件故障。假设重启软件的时间为5分钟,修复硬件的时间为1小时。

#### 答案

我们可以通过计算每个组件故障导致的停机时间来估算服务的可用性。我们将保守地选取图6.1中每个类别的最低值,并将1000次停机均匀分配到四个组件之间。我们忽略慢速磁盘——1000次停机中的第五个组件——因为它们影响性能但不影响可用性,同时也忽略电力公用事业故障,因为不间断电源(UPS)系统隐藏了99%的故障。

没有软件冗余来掩盖众多故障,这2400台服务器上的服务平均每周会停机一天——零个“九”,这远低于WSCs的目标可用性99.99%。

根据第6.10节的解释,Web搜索计算中心(WSCs)的前身是计算机集群。集群是通过局域网(LAN)和交换机连接在一起的独立计算机集合。在不需要大量通信的工作负载中,集群提供了比共享内存多处理器更具成本效益的计算能力。(共享内存多处理器是第5章讨论的多核计算机的前身。)在1990年代末,集群在科学计算中变得流行,随后也用于互联网服务。对于WSCs的一种看法是,它们只是从数百台服务器的集群逻辑演变到数万台服务器的结果。

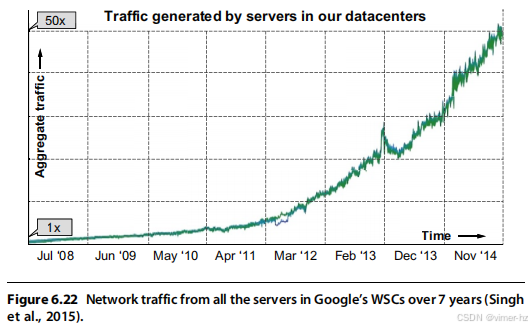

一个自然的问题是,WSCs是否与现代高性能计算(HPC)集群相似。尽管某些HPC设计在规模和成本上相似——有些设计拥有百万个处理器,花费数亿美元——但从历史上看,它们的处理器更强大,并且节点之间的网络延迟远低于WSCs,这是因为HPC应用程序的相互依赖性更强,并且通信更加频繁(见第6.3节)。编程环境还强调线程级并行或数据级并行(见第4章和第5章),通常关注完成单个任务的延迟,而不是通过请求级并行完成多个独立任务的带宽。此外,HPC集群通常会有长时间运行的作业,使得服务器能够充分利用,即使长达数周之久。WSC(Web搜索计算中心)中的服务器利用率通常在10%到50%之间(见第441页的图6.3),并且每天都在变化。与超级计算机环境不同,数千名开发人员共同维护WSC的代码库,并每周部署重要的软件版本(Barroso等,2017)。

那么,WSC与传统数据中心相比如何呢?传统数据中心的运营者一般会从组织的多个部分收集机器和第三方软件,并为其他人集中运行这些资源。他们的主要关注点往往是将许多服务整合到更少的机器上,这些机器彼此隔离以保护敏感信息。因此,虚拟机在数据中心中变得越来越重要。虚拟机对WSC同样重要,但它们扮演着不同的角色。虚拟机用于在不同客户之间提供隔离,并将硬件资源划分为不同大小的份额,以便以多种价格点进行租赁(见第6.5节)。与WSC不同,传统数据中心通常具有大量的硬件和软件异构性,以服务于组织内部不同客户的需求。WSC程序员会自定义第三方软件或构建自己的软件,而WSC则拥有更为同质的硬件;WSC的目标是使仓库中的硬件/软件像一台单一计算机那样运行多种应用程序。通常,传统数据中心最大的成本是维护这些设施的人力,而正如我们将在第6.4节中看到的,在设计良好的WSC中,服务器硬件是最大的成本,人力成本则从最高层转移到最低层。传统数据中心的规模也无法与WSC相比,因此无法获得前面提到的规模经济效益。

因此,尽管WSC可以被视为一种极端的数据中心,因为计算机在具有特殊电气和冷却基础设施的空间中单独安置,但在架构和运营上,传统数据中心与WSC面临的挑战和机遇几乎没有共同之处。

我们将从WSC的工作负载和编程模型开始介绍。

6.2 Programming Models and Workloads for Warehouse-Scale Computers

如果一个问题没有解决方案,它可能不是一个问题,而是一个事实——不是要被解决,而是要随着时间来应对。

—— 西蒙·佩雷斯

除了公共互联网服务,如搜索、视频分享和社交网络,这些服务使它们声名显赫,WSC(Web搜索计算中心)还运行批处理应用程序,例如将视频转换为新格式或从网页抓取中创建搜索索引。

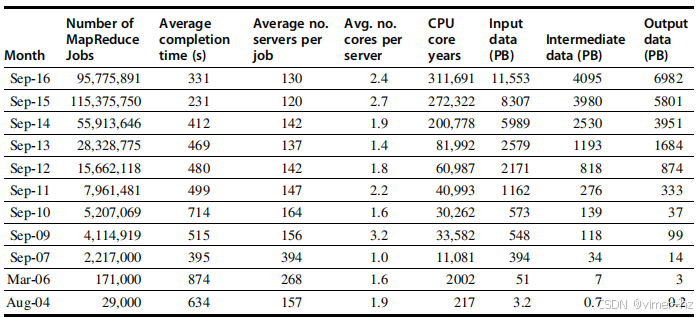

在WSC中,一个流行的批处理框架是MapReduce(Dean 和 Ghemawat, 2008)及其开源版本Hadoop。图6.2显示了MapReduce在谷歌上的日益普及。MapReduce受到同名Lisp函数的启发,Map首先将程序员提供的函数应用于每个逻辑输入记录。Map在数百台计算机上运行,以生成键值对的中间结果。Reduce收集这些分布式任务的输出,并使用另一个程序员定义的函数将其合并。假设Reduce函数是可交换和结合的,它可以在对数时间内运行。借助适当的软件支持,这两个函数既快速又易于理解和使用。在30分钟内,一位初学者就可以在数千台计算机上运行MapReduce任务。

图6.2 显示了2004年至2016年间谷歌的每月MapReduce使用情况。在12年中,MapReduce作业的数量增加了3300倍。页面461的图6.17估计,在亚马逊的云计算服务EC2上运行2016年9月的工作负载将耗费1.14亿美元。更新自Dean, J., 2009年。构建大型分布式系统的设计、经验和建议 [主题演讲]。收录于:第三届ACM SIGOPS国际大型分布式系统与中间件研讨会论文集,与第22届ACM操作系统原理研讨会共同举办,2009年10月11-14日,蒙大拿州大天空。

图6.2显示了平均作业使用了数百台服务器。除了少数来自高性能计算的高度优化应用程序外,这类MapReduce作业是目前最并行的应用,无论是按总CPU时间还是所使用的服务器数量进行测量。

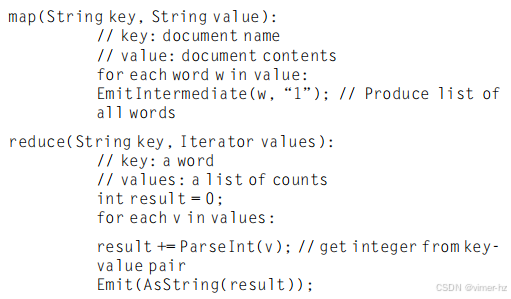

以下是一个MapReduce程序,它计算在一大堆文档中每个英语单词的出现次数。下面是该程序的简化版本,仅显示内部循环,并假设文档中仅找到一个英语单词的出现(Dean 和 Ghemawat, 2008):

在Map函数中使用的EmitIntermediate函数会将文档中的每个单词及其值“1”发出。然后,Reduce函数使用ParseInt()对每个文档中每个单词的所有值进行求和,以获取在所有文档中每个单词的出现次数。MapReduce运行时环境将映射任务和归约任务调度到WSC的节点上。(程序的完整版本见Dean和Ghemawat(2008))。

MapReduce可以被视为单指令流、多数据流(SIMD)操作的推广(第4章),不同之处在于要应用的函数会传递给数据,随后是一个用于减少Map任务输出的函数。由于在SIMD程序中归约操作非常常见,SIMD硬件通常提供特殊的归约操作。例如,英特尔的AVX SIMD指令包括“水平”指令,用于加法操作,处理寄存器中相邻的操作数对。

为了适应数百台计算机性能的变异性,MapReduce调度器根据节点完成先前任务的速度分配新任务。显然,单个缓慢的任务可能会拖延大型MapReduce作业的完成。Dean和Barroso(2013)将这种情况称为尾延迟。在WSC中,解决慢任务的方法是提供软件机制来应对这种在该规模下固有的变异性。这一方法与传统数据中心中服务器的解决方案形成鲜明对比,后者通常认为慢任务意味着硬件故障需要更换,或者服务器软件需要调整和重写。在WSC中,50000至100000台服务器的性能异质性是常态。例如,在MapReduce程序的末尾,系统会开始在其他节点上备份尚未完成的任务,并从完成最快的任务中获取结果。通过增加资源使用率几个百分点,Dean和Ghemawat(2008)发现一些大型任务的完成速度提高了30%。

可靠性从一开始就被纳入MapReduce的设计中。例如,MapReduce作业中的每个节点都需要定期向主节点报告已完成任务的列表和更新状态。如果某个节点未在截止时间前报告,主节点会认为该节点已死,并将该节点的工作重新分配给其他节点。鉴于WSC中的设备数量,故障的普遍存在并不令人惊讶,正如之前的示例所示。为了实现99.99%的可用性,系统软件必须在WSC中应对这一现实。为了降低运营成本,所有WSC都使用自动监控软件,使一个操作员能够负责超过1000台服务器。

编程框架,如用于批处理的MapReduce和面向外部的SaaS(软件即服务)如搜索,引依赖于内部软件服务以实现成功。例如,MapReduce依赖于Google文件系统(GFS)(Ghemawat等,2003)或Colossus(Fikes,2010)来为任何计算机提供文件,以便在任何地方调度MapReduce任务。

除了GFS和Colossus,这些可扩展存储系统的例子还包括亚马逊的键值存储系统Dynamo(DeCandia等,2007)和谷歌的记录存储系统BigTable(Chang等,2006)。注意,这些系统通常是建立在彼此之上的。例如,BigTable将其日志和数据存储在GFS或Colossus上,就像关系数据库可能使用内核操作系统提供的文件系统一样。

这些内部服务通常做出与单服务器上运行的类似软件不同的决策。例如,与假设存储是可靠的(例如使用RAID存储服务器)不同,这些系统通常会创建数据的完整副本。副本可以帮助提高读取性能和可用性;通过适当的放置,副本能够克服许多其他系统故障,如图6.1所示。像Colossus这样的系统使用纠错码而不是完整副本来降低存储成本,但其不变的是跨服务器的冗余,而不是服务器内部或存储阵列内部的冗余。因此,整个服务器或存储设备的故障不会对数据的可用性产生负面影响。

另一种不同的方法是WSC存储软件通常使用放宽的一致性,而不是遵循传统数据库系统的所有ACID(原子性、一致性、隔离性和持久性)要求。其洞察在于,多个数据副本在某个时刻一致很重要,但对大多数应用而言,它们并不需要始终保持一致。例如,对于视频共享来说,最终一致性是可以接受的。最终一致性使存储系统更易于扩展,这是WSC的绝对要求。

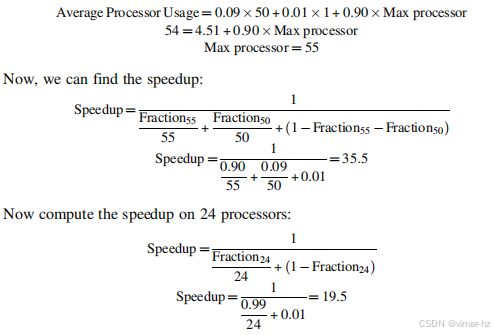

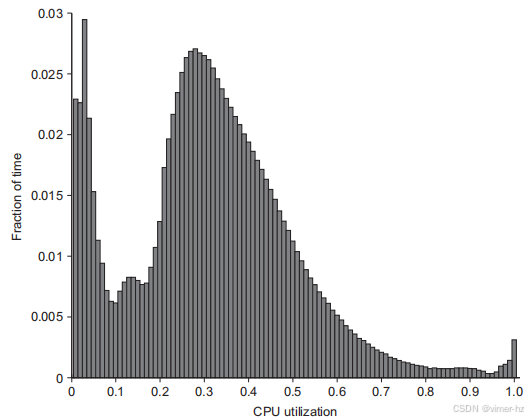

这些公共交互服务的工作负载需求各不相同;甚至像谷歌搜索这样显著的全球服务,其需求随时间变化可达到两倍的差异。在考虑周末、假期以及某些应用(例如元旦后的照片共享服务或圣诞节前的在线购物)的热门时段时,服务器利用率的变化更加明显。图6.3显示了5000台谷歌服务器在6个月期间的平均利用率。请注意,少于0.5%的服务器平均达到100%利用率,大多数服务器的利用率在10%到50%之间。换句话说,仅有10%的服务器利用率超过50%。因此,在WSC中,服务器在低负载时表现良好比在高峰时高效更为重要,因为它们很少处于高峰状态。

图6.3 显示了在谷歌超过5000台服务器在6个月期间的平均CPU利用率。这些服务器很少完全闲置或完全利用,而是在大多数时间内以其最大利用率的10%到50%之间运行。图6.4中右侧的第三列计算了上下浮动5%的百分比来得出加权,因此90%这一行的1.2%意味着有1.2%的服务器的利用率在85%到95%之间。数据来源于Barroso, L.A., Holzle, U., 2007年的文章《能量比例计算的案例》。IEEE Computing. 40 (12), 33–37。

总之,WSC的硬件和软件必须应对基于用户需求的负载变化以及由于硬件在这种规模下的不确定性而导致的性能和可靠性变化。

示例:根据图6.3中的测量结果,SPECpower基准测试从0%负载到100%以10%的增量测量功耗和性能(见第1章)。该基准测试的总体单一指标是所有性能测量(每秒服务器端Java操作)的总和除以所有功耗测量(以瓦特为单位)的总和。因此,假设每个级别的可能性是相等的。如果根据图6.3中的利用率频率对这些级别进行加权,这些数值摘要指标将如何变化?

答案:图6.4显示了原始加权和与图6.3匹配的新加权。这些加权将性能摘要减少了30%,从3210 ssj_ops/watt降至2454。

考虑到规模,软件必须处理故障,这意味着几乎没有理由购买“镀金”的硬件来减少故障频率。主要的影响将是成本上升。Barroso和Hölzle(2009)发现,在运行TPC-C数据库基准测试时,高端惠普共享内存多处理器与普通惠普服务器之间的性价比相差20倍。不出所料,谷歌和所有其他拥有WSC(Web Server Cluster)公司的选择都是低端普通服务器。事实上,开放计算项目(http://opencompute.org)是一个这样的组织,致力于让这些公司共同合作,设计开放式的数据中心服务器和机架。

这些WSC服务通常倾向于开发自己的软件,而不是购买第三方商业软件,部分原因是为了应对巨大的规模,部分原因是为了节省成本。例如,即使在2017年TPC-C的最佳性价比平台上,添加SAP SQL Anywhere数据库和Windows操作系统的成本也会使Dell PowerEdge T620服务器的费用增加40%。相比之下,谷歌在其服务器上运行BigTable和Linux操作系统,因此无需支付许可费用。

在回顾了WSC的应用和系统软件之后,我们准备来看看WSC的计算机架构。

6.3 Computer Architecture of Warehouse-Scale Computers

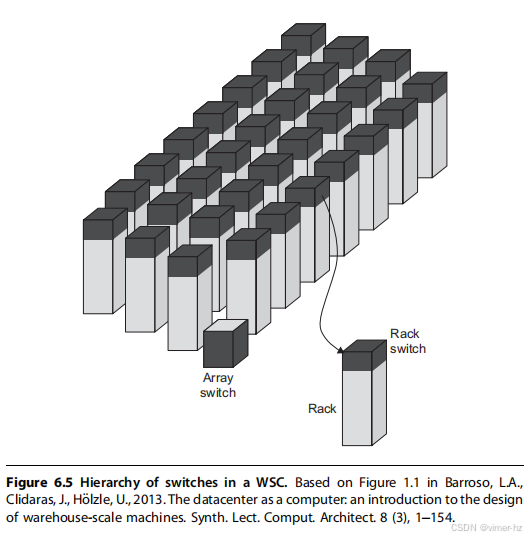

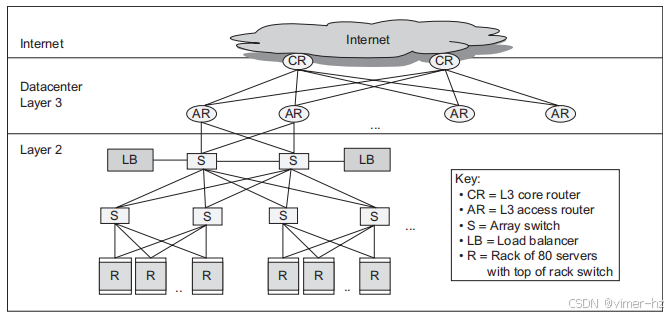

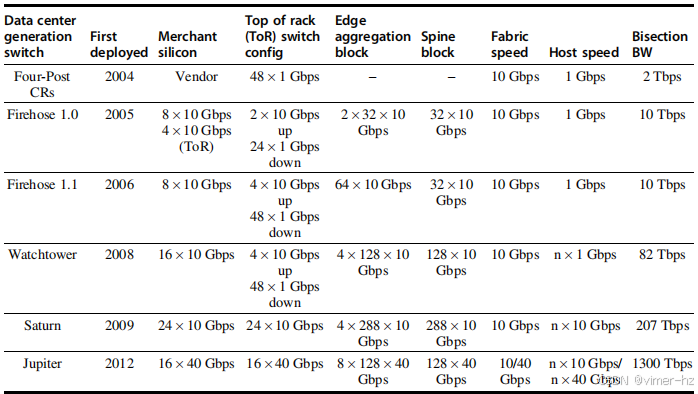

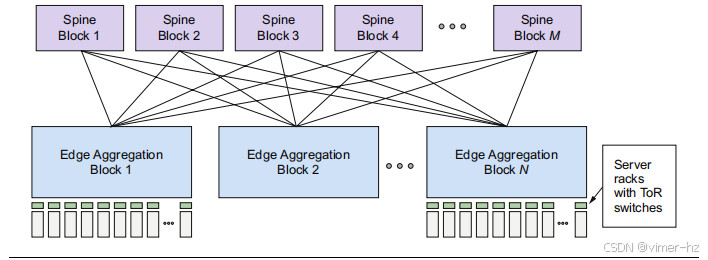

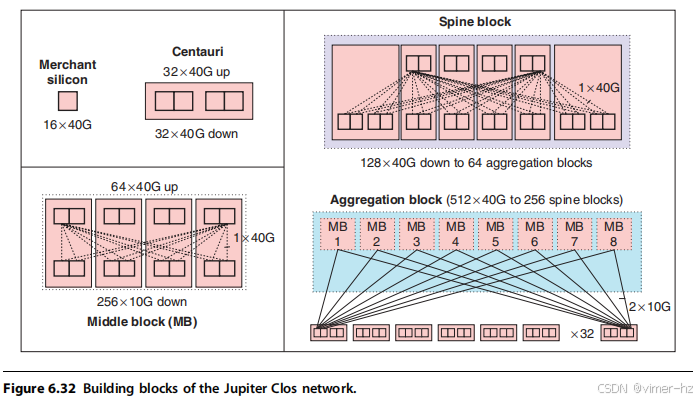

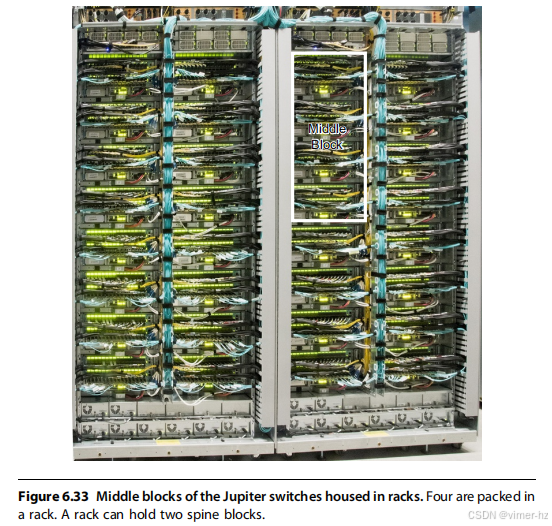

网络是将50,000到100,000台服务器连接在一起的“连接组织”。类似于第二章中提到的内存层次结构,WSC(Web Server Cluster)使用了一种网络层次结构。图6.5展示了一个例子。理想情况下,综合网络能够提供接近为10万台服务器定制的高端交换机的性能,而成本则大约相当于为50台服务器设计的商品交换机的每个端口费用。正如我们将在第6.6节中看到的,WSC的网络是一个活跃创新的领域。

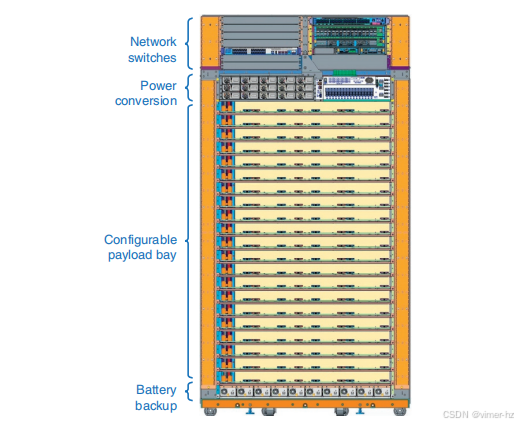

支撑服务器的结构是机架。尽管不同WSC的机架宽度各不相同——有些是经典的19英寸宽机架;其他的可能宽出两到三倍——但是高度通常不超过6到7英尺,因为需要有人来维护它们。这样的机架大约可以容纳40到80台服务器。由于在机架顶部连接网络电缆通常更为方便,因此这个交换机通常被称为机架顶端交换机(Top of Rack, ToR)。 (一些WSC有多个ToR交换机的机架。)

通常,机架内部的带宽远高于机架之间的带宽,因此如果发送者和接收者位于同一机架中,软件放置它们的位置就不那么重要。这种灵活性从软件的角度来看是理想的。这些交换机通常提供4到16个上行链路,连接到网络层次结构中的下一个更高的交换机。因此,离开机架的带宽是机架内部带宽的6到24倍更小。这个比率被称为超额订阅(oversubscription)。然而,大量的超额订阅意味着程序员在将发送者和接收者放置在不同机架时必须意识到性能的影响。这种增加的软件调度负担是专门为数据中心设计的网络交换机的另一个理由。

连接一系列机架的交换机相较于机架顶端交换机(ToR)要昂贵得多。这部分成本是由于更高的连接性,以及为了减少超额订阅问题,交换机的带宽必须大得多。Barroso等(2013)报告称,具有机架交换机10倍分割带宽——即基本上是最坏情况下的内部带宽——的交换机成本约为机架交换机的100倍。原因之一是交换机的带宽成本随着端口数量n的增加而增长,呈现n²的关系。第6.6节和第6.7节将详细描述ToR交换机以上的网络结构。

存储

一种自然的设计是填满机架中的服务器,除去为交换机保留的空间。这种设计留下了存储放置位置的问题。从硬件构建的角度来看,最简单的解决方案是在机架内包含磁盘,并依靠以太网连接来访问远程服务器上的信息。一个昂贵的替代方案是使用网络附加存储(NAS),可能通过如InfiniBand这样的存储网络。在过去,WSC通常依赖本地磁盘,并提供处理连接性和可靠性的存储软件。例如,GFS使用本地磁盘并维护副本,以克服可靠性问题。这种冗余不仅覆盖了本地磁盘故障,还包括对机架和整个集群的电源故障。GFS的最终一致性灵活性降低了保持副本一致性的成本,也减少了存储系统的网络带宽需求。

如今的存储选项更加多样化。尽管一些机架在服务器和磁盘之间达到了平衡,如同过去一样,也可能存在没有本地磁盘的机架,以及装满磁盘的机架。现代系统软件通常使用类似RAID的错误修正编码来降低可靠性的存储成本。

需要注意的是,在讨论WSC架构时,“集群”一词常常会引起混淆。根据第6.1节的定义,WSC只是一个极大的集群。相反,Barroso等(2013)使用“集群”一词来指代下一个规模的计算机组合,包含许多机架。在本章中,为了避免混淆,我们将使用“阵列”一词来表示以行组织的大型机架集合,同时保留“集群”一词的原始定义,用以表示从机架内联网计算机的集合到充满联网计算机的整个仓库。

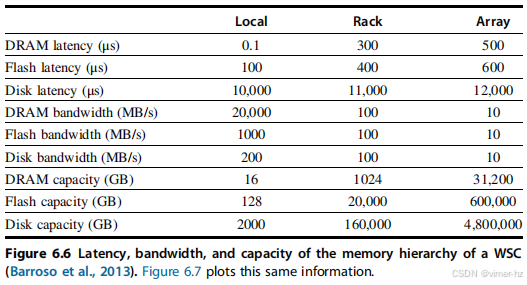

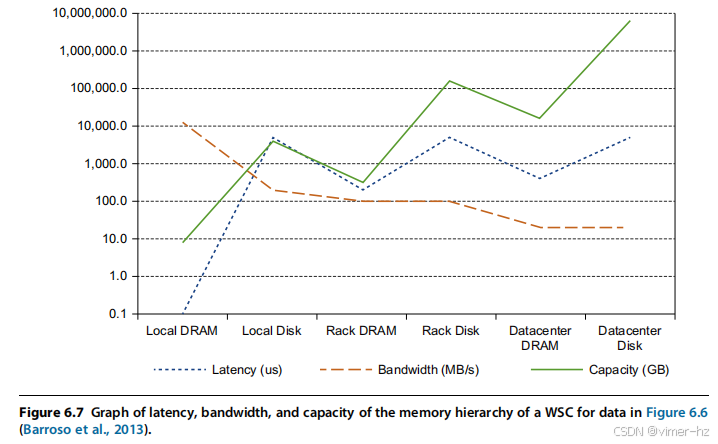

### WSC 内存层次结构

图 6.6 显示了 WSC 内部内存层次结构的延迟、带宽和容量,图 6.7 则以视觉方式展示了相同的数据。这些图基于以下假设(Barroso 等,2013):

- 每台服务器包含 16 GiB 的内存,访问时间为 100 纳秒,传输速率为 20 GB/s;128 GiB 的闪存,延迟为 100 微秒,传输速率为 1 GB/s;以及 2 TB 的磁盘,访问时间为 10 毫秒,传输速率为 200 MB/s。每块板上有两个插槽,它们共享一个 1 Gbit/s 的以太网端口。

- 在这个例子中,每对机架包括一个机架交换机,并包含 80 台服务器。网络软件加上交换机的开销将 DRAM 的延迟增加到 100 微秒,将磁盘访问延迟增加到 11 毫秒。因此,一个机架的总存储容量大约为 1 TB 的 DRAM、20 TB 的闪存和 160 TB 的磁盘存储。1 Gbit/s 的以太网限制了机架内远程访问 DRAM、闪存或磁盘的带宽为 100 MB/s。

- 阵列由 30 个机架组成,因此阵列的存储容量增长了 30 倍:30 TB 的 DRAM、600 TB 的闪存和 4.8 PB 的磁盘。阵列交换机的硬件和软件将阵列内部 DRAM 的延迟增加到 500 微秒,闪存为 600 微秒,磁盘延迟为 12 毫秒。阵列交换机的带宽限制了远程访问阵列 DRAM、阵列闪存或阵列磁盘的带宽为 10 MB/s。

图 6.6 和 6.7 显示,网络开销显著增加了局部 DRAM 和闪存、机架 DRAM 和闪存、或阵列 DRAM 和闪存之间的延迟,但所有这些仍然比访问本地磁盘的延迟好 10 倍以上。网络缩小了机架 DRAM、闪存与磁盘之间,以及阵列 DRAM、闪存与磁盘之间的带宽差异。

图 6.8 显示了用于将阵列连接在一起并与互联网连接的第 3 层网络(Greenberg 等,2009)。负载均衡器监控一组服务器的繁忙程度,并将流量引导到负载较轻的服务器,以尽量保持服务器的利用率大致相同。另一种选择是使用单独的边界路由器将互联网连接到数据中心的第 3 层交换机。如我们将在第 6.6 节看到的,许多现代 WSC 已经放弃了传统交换机的常规分层网络架构。

WSC 需要 40 个阵列才能达到 100,000 台服务器,因此网络层次结构中还有一个层级。图 6.8 显示了常规的三层路由器,用于将阵列连接在一起并与互联网连接。

大多数应用程序适合在 WSC 中的单个阵列内运行。那些需要多个阵列的应用采用分片或分区的方法,这意味着数据集被拆分为独立的部分,然后分发到不同的阵列中。可以将其类比为注册会议时,由一个人处理 A 到 M 的名字,另一个人处理 N 到 Z。对整个数据集的操作被发送到托管这些部分的服务器,结果由客户端计算机汇总。

**示例**:假设 90% 的访问是本地于服务器,9% 是在机架内但不在服务器内,1% 是在机架外但仍在阵列内,平均内存延迟是多少?

**答案**:平均内存访问时间为:

![]()

这比 100% 本地访问的情况慢了超过 300 倍。显然,服务器内的访问局部性对 WSC 性能至关重要。

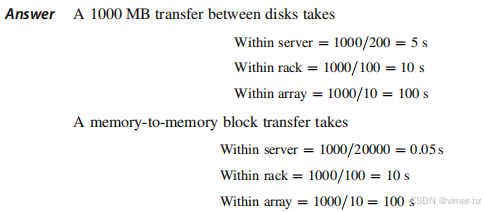

**示例**:在服务器内部、机架内的服务器之间,以及阵列中不同机架之间,传输 1000 MB 的数据需要多长时间?在这三种情况下,DRAM 之间传输 1000 MB 的速度又快多少?

因此,对于单个服务器外的块传输,数据是存储在内存中还是在磁盘上并不重要,因为机架交换机和阵列交换机是瓶颈。这些性能限制影响了 WSC 软件的设计,并促使对更高性能交换机的需求(见第 6.6 节)。

虽然这些例子具有教育意义,但请注意,计算机和网络设备的规模和速度可能远大于这些来自 2013 年的示例(见第 6.7 节)。到 2017 年,服务器的 DRAM 部署已达到 256–1024 GiB,而最近的交换机将延迟降低到了每跳仅 300 纳秒。考虑到 IT 设备的架构,我们现在可以讨论如何为其布置、供电和降温,以及与仅仅在其中的 IT 设备相比,构建和运营整个 WSC 的成本。

6.4 The Efficiency and Cost of Warehouse-Scale Computers

基础设施成本,包括电力分配和冷却,是 WSC 建设成本的主要部分,因此我们将重点讨论这些内容。(第 6.7 节详细描述了 WSC 的电力和冷却基础设施。)

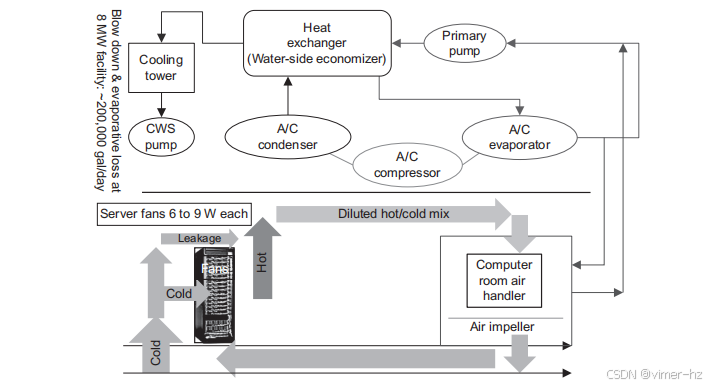

计算机房空调(CRAC)单元通过冷却水来冷却服务器房间的空气,类似于冰箱通过将热量释放到外部来去除热量。当液体吸收热量时,它就会蒸发。相反,当液体释放热量时,它会凝结。空调将液体泵送到低压线圈中以蒸发并吸收热量,然后将其送到外部冷凝器进行释放。因此,在 CRAC 单元中,风扇将温暖的空气推过一组充满冷水的线圈,泵则将加热后的水输送到制冷设备进行冷却。图 6.9 显示了大量的风扇和水泵,它们在系统中移动空气和水。

图 6.9 冷却系统的机械设计。CWS 代表循环水系统。来源于 Hamilton, J., 2010。云计算的规模经济。在:2010 年 6 月 8 日在华盛顿州西雅图举办的 AWS 基因组学与云计算研讨会上提交的论文。http://mvdirona.com/jrh/TalksAndPapers/JamesHamilton_GenomicsCloud20100608.pdf。

除了制冷设备,一些数据中心利用较冷的外部空气或水温在水送往制冷设备之前进行预冷。然而,根据地点的不同,在一年中的温暖时期,制冷设备仍可能是必需的。令人惊讶的是,如何在考虑电力分配和冷却的开销后,计算一个 WSC 能支持多少台服务器并不明显。来自服务器制造商的额定功率总是比较保守:这是服务器能够消耗的最大功率。因此,第一步是在多种工作负载下测量单个服务器的功率,以便在 WSC 中部署。(网络通常占总功耗的约 5%,因此在初期可以忽略。)

为了确定 WSC 的服务器数量,可将可用于 IT 设备的电力除以测得的单台服务器功率;然而,根据 Fan 等人的研究(2007),这仍然过于保守。他们发现,在理论上,成千上万台服务器在最坏情况下可以做到的与它们在实际中会做到的之间存在显著差距,因为没有真实的工作负载会使成千上万台服务器同时达到其峰值。他们发现,可以根据单台服务器的功率安全地超额订阅多达 40% 的服务器数量。他们建议 WSC 设计师这样做,以提高 WSC 内电力的平均利用率;但他们也建议使用广泛的监控软件以及安全机制,在工作负载变化时取消调度低优先级任务。

以下是 2012 年在 Google WSC 中的 IT 设备内部的电力使用情况(Barroso et al., 2013):

测量 WSC 的效率

评估数据中心或 WSC 效率的一种广泛使用的简单指标称为电力利用效率(PUE):

![]()

因此,PUE 必须大于或等于 1,PUE 越大,WSC 的效率越低。

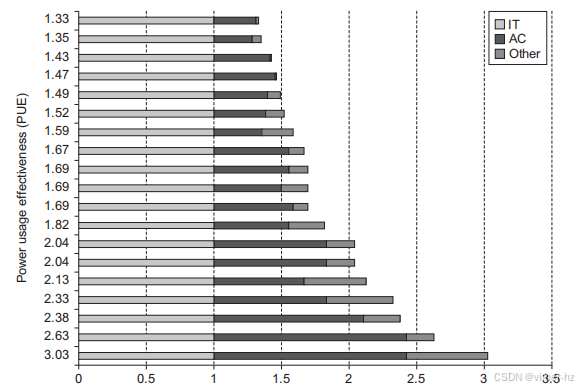

Greenberg 等人(2009)对 19 个数据中心的 PUE 和用于冷却基础设施的开销部分进行了报告。图 6.10 显示了他们的发现,按 PUE 从高到低排序。中位数 PUE 为 1.69,冷却基础设施使用的电力超过服务器的一半——平均而言,1.69 中有 0.55 是用于冷却。需要注意的是,这些是平均 PUE,可能会因工作负载甚至外部空气温度的变化而每天有所不同,如我们将看到的(图 6.11)。

图 6.10 2006 年 19 个数据中心的电力利用效率(Greenberg 等,2009)。在计算 PUE 时,空调(AC)和其他用途(如电力分配)的电力被归一化为 IT 设备的电力。因此,IT 设备的电力必须为 1.0,而空调的电力大约在 IT 设备电力的 0.30 到 1.40 倍之间。“其他”用途的电力大约占 IT 设备的 0.05 到 0.60 倍。

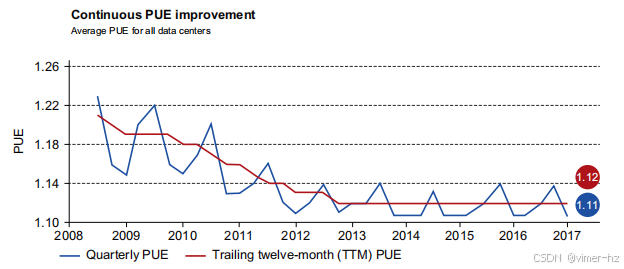

图 6.11 2008 年至 2017 年间 15 个 Google WSC 的平均电力利用效率(PUE)。波动的线条表示季度平均 PUE,而相对平直的线条表示过去 12 个月的平均 PUE。对于 2016 年第四季度,平均值分别为 1.11 和 1.12。

在过去十年中,随着对 PUE 的关注,数据中心的效率大大提高。然而,正如第 6.8 节所解释的,关于 PUE 的包含内容尚无普遍接受的定义:如果用于在停电时保持运行的电池位于单独的建筑中,它们是否应被计算在内?你是从电力变电站的输出测量,还是从电力首次进入 WSC 的地方测量?图 6.10 显示了所有 Google 数据中心平均 PUE 的随时间变化的改善,而这个 PUE 是 Google 综合测量的。

由于每美元的性能是最终指标,我们仍然需要测量性能。如图 6.7 所示,带宽下降和延迟增加取决于与数据的距离。在 WSC 中,服务器内的 DRAM 带宽是机架内的 200 倍,而机架内又是阵列内的 10 倍。因此,在 WSC 内数据和程序的放置上,还有另一种局部性需要考虑。

尽管 WSC 的设计师通常关注带宽,但在 WSC 上开发应用程序的程序员也关心延迟,因为延迟是用户可以感知到的。用户的满意度和生产力与服务的响应时间密切相关。一些关于时间共享时代的研究报告显示,用户生产力与交互时间成反比,交互时间通常分为人机输入时间、系统响应时间以及用户在按下下一个输入前思考响应所需的时间(Doherty 和 Thadhani,1982)。实验结果表明,将系统响应时间缩短 30% 可以将交互时间缩短 70%(Brady,1986)。这一看似不合理的结果可以用人性来解释:当给出更快的响应时,人们思考所需的时间更少,因为他们不太可能分心,能够保持“状态”。

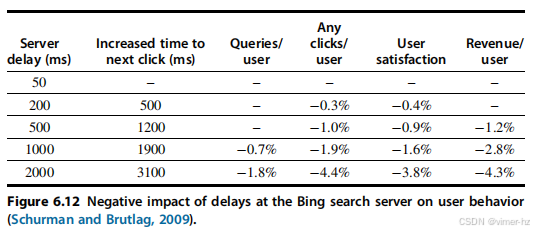

图 6.12 显示了针对 Bing 搜索引擎的一项较新实验的结果,该实验在搜索服务器上插入了 50-2000 毫秒的延迟(Schurman 和 Brutlag,2009)。与之前的研究结果一致,下一次点击的时间大约翻倍了延迟;也就是说,服务器上的 200 毫秒延迟导致下一次点击时间增加 500 毫秒。随着延迟的增加,收入呈线性下降,用户满意度也随之降低。另一项关于 Google 搜索引擎的独立研究发现,这些影响在为期 4 周的实验结束后仍然持续。五周后,经历 200 毫秒延迟的用户每天的搜索人数减少了 0.1%,而经历 400 毫秒延迟的用户搜索次数则减少了 0.2%。考虑到搜索带来的巨大收益,即使是如此微小的变化也令人不安。事实上,结果如此消极,以至于他们提前结束了实验。

由于对互联网服务所有用户满意度的极度关注,性能目标通常会被设定为确保高比例的请求低于某个延迟阈值,而不仅仅是针对平均延迟设定目标。这样的阈值目标被称为服务水平目标(SLOs)。例如,一个 SLO 可能规定 99% 的请求必须低于 100 毫秒。因此,亚马逊的 Dynamo 键值存储系统的设计者决定,为了在 Dynamo 上提供良好的延迟,他们的存储系统必须在 99.9% 的时间内达到其延迟目标(DeCandia 等,2007)。例如,Dynamo 的一项改进帮助了 99.9 百分位的性能,远超过平均情况,这反映了他们的优先事项。

Dean 和 Barroso(2013)提出了“尾容忍”这一术语,用来描述旨在满足此类目标的系统:就像容错计算旨在将不太可靠的部分构建成一个可靠的整体,大型在线服务需要从不太可预测的部分中创建一个可预测的响应整体。

造成不可预测性的原因包括对共享资源(处理器、网络等)的争用、排队、由于 Turbo 模式或动态电压频率调整(DVFS)等优化引起的微处理器性能波动、软件垃圾回收等等。谷歌得出的结论是,与其试图防止 WSC 中的这种可变性,不如开发尾容忍技术来掩盖或绕过临时的延迟峰值。例如,细粒度负载均衡可以快速在服务器之间移动小量工作,从而减少排队延迟。

### WSC的成本

如引言中所提到的,与大多数架构师不同,WSC的设计者不仅关注建造WSC的成本,还关注其运营成本。会计将前者称为运营支出(OPEX),将后者称为资本支出(CAPEX)。

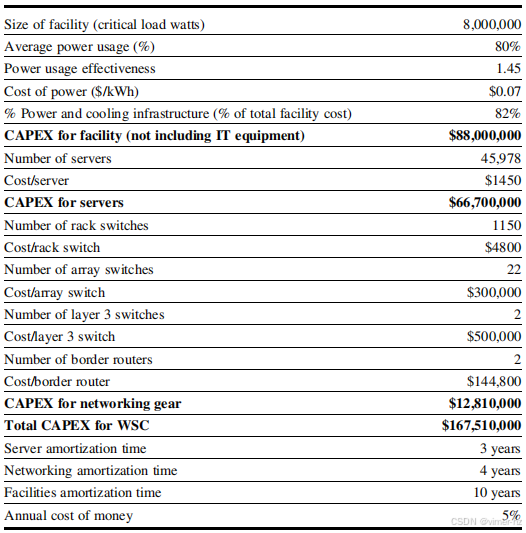

为了更好地理解能源成本,Hamilton(2010)进行了一项案例研究以估算WSC的成本。他确定一个8兆瓦(MW)设施的CAPEX为8800万美元,约46000台服务器和相应的网络设备又增加了7900万美元的CAPEX。图6.13显示了该案例研究的其他假设。

图6.13 WSC案例研究,四舍五入到最近的5000美元。互联网带宽成本因应用而异,因此未在此包含。设施的剩余18% CAPEX包括购买物业和建筑成本。我们在图6.14中添加了安全和设施管理的人力成本,这些并不在案例研究中。请注意,Hamilton的估算是在他加入亚马逊之前进行的,且并不是基于某个特定公司的WSC。参考文献:Hamilton, J., 2010. 云计算规模经济。发表于2010年6月8日,在华盛顿州西雅图举行的AWS基因组学与云计算研讨会上。http://mvdirona.com/jrh/TalksAndPapers/JamesHamilton_GenomicsCloud20100608.pdf。

Hamilton的研究结果显示建筑、电力和冷却的成本为每瓦11美元。Barroso等人(2013)在多个案例中报告了相似的结果,成本为每瓦9到13美元。因此,一个16 MW的设施成本为1.44亿到2.08亿美元,不包括计算、存储和网络设备的费用。

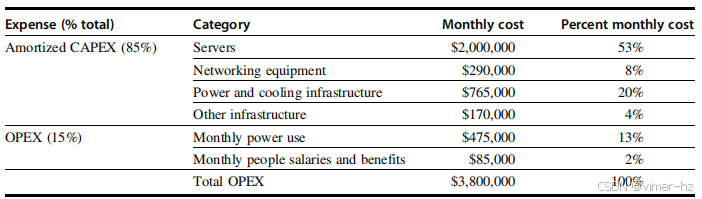

我们可以通过资本成本转换将CAPEX转换为OPEX,假设借款成本为5%,这是美国会计规则中的标准惯例。也就是说,我们可以将CAPEX作为固定金额在设备的有效使用寿命内每月摊销。图6.14详细列出了Hamilton案例研究的每月OPEX。请注意,他的案例研究中,摊销率差异显著:设施为10年,网络设备为4年,服务器为3年。因此,WSC设施的使用寿命为十年,但服务器每3年更换一次,网络设备每4年更换一次。通过摊销CAPEX,Hamilton得出了每月OPEX,包括借款成本(年利率5%)来支付WSC的费用。每月OPEX为380万美元,约占CAPEX的2%(或年均24%)。

这个数据为我们提供了一个实用的指导原则,以便在关注能源时做出关于使用哪些组件的决策。在WSC中,每年的完全负担成本(包括电力和冷却基础设施的摊销成本)为每瓦...

![]()

成本大约为每瓦每年2美元。因此,通过节能降低成本不应导致支出超过每瓦每年2美元(见第6.8节)。注意,在图6.14中,超过三分之一的运营支出(OPEX)与电力相关,该类别的支出呈上升趋势,而服务器成本则在下降。网络设备占总OPEX的8%和服务器CAPEX的19%,而且网络设备的成本下降速度不如服务器快,这可能是由于对更高网络带宽的持续需求(见第467页的图6.22)。这种差异在机架上方的网络层次结构中的交换机尤其明显,它们代表了大部分网络成本(见第6.6节)。安全和设施管理的人力成本仅占OPEX的2%。将图6.14中的OPEX除以服务器数量和每月的小时数,成本约为每台服务器每小时0.11美元。

图6.14 图6.13的每月运营支出(OPEX),四舍五入到最近的5000美元。注意,服务器的3年摊销意味着每3年购买新的服务器,而设施的摊销期为10年。因此,服务器的摊销资本成本约为设施的三倍。人力成本包括三名保安职位,全天24小时、全年365天,每人每小时20美元,以及一名设施管理人员,全天24小时、全年365天,每小时30美元。员工福利为薪资的30%。此计算未包括互联网的网络带宽费用,因为它因应用而异,也未包括供应商维护费用,因为这些费用因设备和谈判而异。

Barroso等(2013)评估了资本支出(CAPEX)和运营支出(OPEX),以每瓦每月的成本进行计算。因此,如果一个12兆瓦(MW)的风能发电系统(WSC)在12年内折旧,折旧成本为每瓦每月0.08美元。他们假设公司通过申请年利率8%的贷款获得WSC的资金——企业贷款通常在7%到12%之间——而利息支付又增加了0.05美元,总计为每瓦每月0.13美元。他们对服务器的成本进行了类似的计算。一台500瓦的服务器成本为4000美元,折合每瓦8美元,4年的折旧为每瓦每月0.17美元。服务器贷款的8%利息又增加了0.02美元。他们估算网络成本为每瓦每月0.03美元。他们报告称,多兆瓦WSC的典型OPEX成本在每瓦每月0.02到0.08美元之间。总成本为每瓦每月0.37到0.43美元。对于一个8兆瓦的WSC,扣除电力成本后的月支出约为300万到350万美元。如果我们从汉密尔顿的计算中减去每月的电力使用,他的月度估算将为330万美元。考虑到预测成本的不同方法,这些估算结果相当一致。

示例:美国各地区电力成本从每千瓦时0.03美元到0.15美元不等。这两种极端价格对每小时服务器成本的影响是什么?

答案:我们将8兆瓦的关键负载乘以图6.13(第二行)的平均PUE,以计算平均功耗:

![]()

电力的月成本因此从图6.14中的475,000美元下降到在每千瓦时0.03美元时的205,000美元,以及在每千瓦时0.15美元时的1,015,000美元。这些电力成本的变化使得每小时的服务器成本分别变为0.11美元、0.10美元和0.13美元。

示例:如果所有折旧时间都统一为5年,月成本会发生什么变化?这将如何改变每台服务器的小时成本?

答案:电子表格可在线访问:http://mvdirona.com/jrh/TalksAndPapers/PerspectivesDataCenterCostAndPower.xls。将折旧时间改为5年后,图6.14的前四行将变为:

总的月运营支出为3,422,000美元。如果我们每5年更换一次所有设备,成本将为每台服务器每小时0.103美元,此时折旧成本更多地用于设施而非服务器,如图6.14所示。

每台服务器每小时约0.10美元的费用相比于许多拥有和运营自己(较小)传统数据中心的公司来说要低得多。WSC的成本优势促使大型互联网公司提供计算服务作为一种公用事业,用户只需为实际使用的部分付费,类似于电力支付。如今,公用计算更广为人知的是云计算。

6.5 Cloud Computing: The Return of Utility Computing

如果我所倡导的计算机成为未来的计算机,那么计算可能会像电话系统一样被组织为公用事业……计算公用事业可能成为一个新兴且重要产业的基础。

——约翰·麦卡锡,麻省理工学院百年庆典(1961年)

随着用户数量不断增加,互联网公司如亚马逊、谷歌和微软从普通组件中构建了越来越大的仓库级计算机,这使得麦卡锡的预测最终成真,但并不是因为他所想的时分共享的普及。这样的需求推动了系统软件的创新,以支持在这一规模下的操作,包括BigTable、Colossus、Dynamo、GFS和MapReduce。同时,这也要求改进运营技术,以确保服务在至少99.99%的时间内可用,即使面对组件故障和安全攻击。这些技术的例子包括故障转移、防火墙、虚拟机以及对分布式拒绝服务攻击的保护。随着软件和专业知识提供了可扩展性,并且客户需求不断增加以证明投资的合理性,拥有50,000到100,000台服务器的WSC在2017年变得司空见惯。

随着规模的扩大,经济效益也随之增加。根据2006年的一项研究,比较了一个WSC与仅有1000台服务器的数据中心,汉密尔顿(2010年)报告了以下优势:

- 存储成本减少5.7倍——WSC的磁盘存储成本为每GB每年4.6美元,而数据中心则为每GB 26美元。

- 行政成本减少7.1倍——WSC的每位管理员所管理的服务器比例超过1000,而数据中心仅为140。

- 网络成本减少7.3倍——WSC的互联网带宽每Mbit/s每月成本为13美元,而数据中心为95美元。不出所料,订购1000 Mbit/s的价格远比订购10 Mbit/s要好得多。

另一个规模经济的来源是在采购过程中。高水平的采购导致WSC几乎所有物品都享有批量折扣价格。

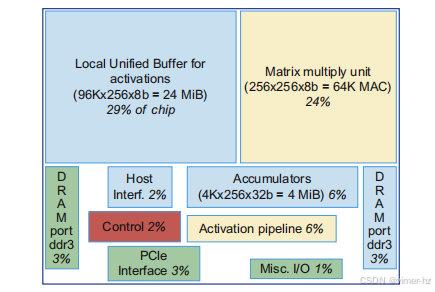

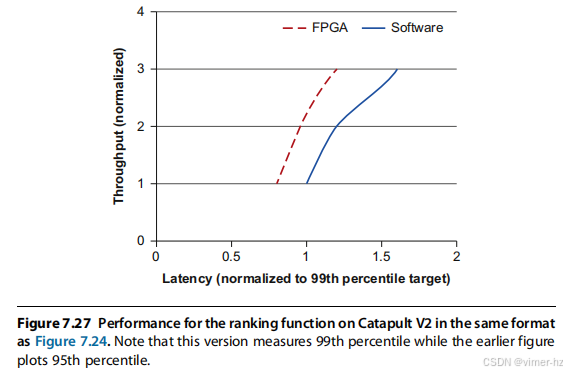

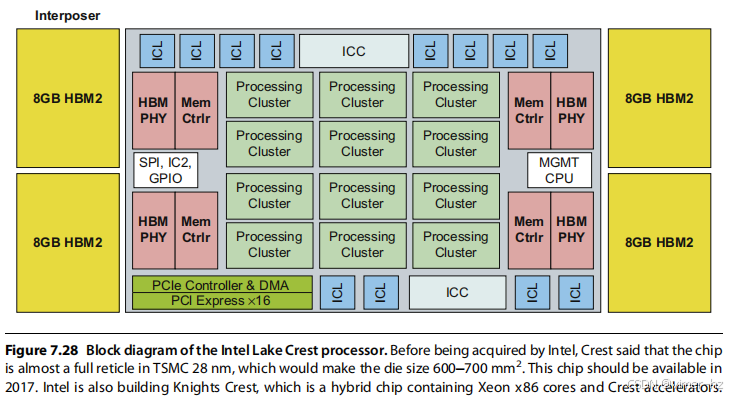

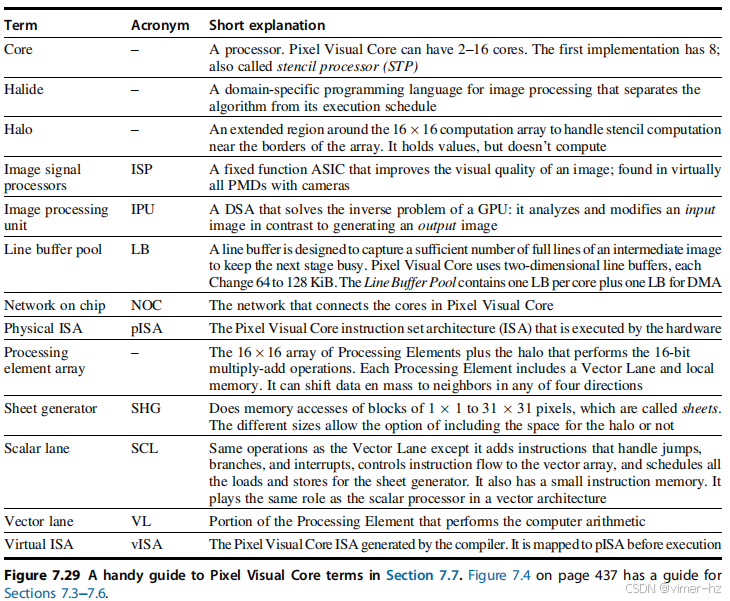

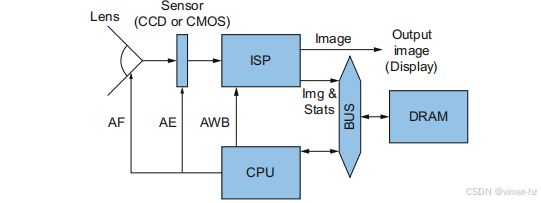

规模经济同样适用于运营成本。从前面的部分我们看到,许多数据中心的PUE(电力使用效率)为2.0。大型企业可以合理地雇佣机械和电力工程师开发PUE在1.1到1.2范围内的WSC(大规模网络数据中心)(见第6.7节)。